# WoW Post-CMOS compatible Cu-Cu Low temperature, Low pressure thermocompression bonding with Pd passivation Engineering.

## WoW Post-CMOS compatible Cu-Cu Low temperature, Low pressure thermocompression bonding with Pd passivation Engineering

C.Hemanth Kumar<sup>1</sup>, Asisa Kumar Panigrahi<sup>1, 2,\*</sup>, Satish Bonam<sup>1</sup>, Nirupam Paul<sup>1</sup>, Sudharshan Vadnala<sup>3</sup>, Siva Rama Krishna Vanjari<sup>1</sup>, and Shiv Govind Singh<sup>1</sup>

<sup>1</sup>Indian Institute of Technology Hyderabad, Department of Electrical Engg., Kandi, India.

<sup>2</sup> KL University H, Department of Electronics & Communication Engg., Hyderabad, India.

<sup>3</sup>Indian Institute of Technology Bombay, Department of Mechanical Engg., Powai, India.

Phone: +91-8332023798, \*E-mail: ee13p1009@iith.ac.in

Abstract— Surface passivation of Copper plays vital role in accomplishing low temperature, low pressure Wafer-on-Wafer (WoW) Cu-Cu thermocompression bonding, as it not only helps in protecting the Cu surface from oxidation but also smoothen the surface. Ultra-thin Palladium (Pd) layer is regarded as one of the promising passivation layer which can prevent oxidation of copper and in addition it can also minimize the roughness of Cu surface. The thickness of Pd layer plays an important role in achieving good and reliable bonding. In this endeavor, we have optimized the Pd passivation thickness to achieve low temperature (150 °C) and low pressure (4 bar) WoW Cu-Cu thermocompression bonding. The optimum thickness of Pd for achieving a good bonding is found out to be 3 nm. Our optimized result yielded an excellent bond interface confirms the reliability of Cu-Cu bonding with Pd passivation.

Keywords: Cu-Cu bonding, Pd Passivation, Thermocompression, 3D IC.

#### 1 Introduction

A Semiconductor industry faces serious technological barrier with interconnect scaling because of ever-growing consumer demand for smaller and faster devices with new functionalities, together there is an exponentially rise in various constraints, which poses serious challenges for Moore's law scaling. Three Dimensional IC (3D IC) integration offer a promising solution by packing a great deal of functionality into small form factors, while improving device performance and reducing the interconnect length without shrinking any device dimension. 3D IC integration is a promising field that addresses the convergence of Moore's Law and More than Moore. It is a stack of several vertically bonded and interconnected thinned IC chips with each other [1]. WoW bonding is one of the most desirable process integration technique to fulfill ever-growing consumer demand to accommodate various functionalities within a smaller foot print without compromising the IC performance. In our previous work, we have demonstrated a low temperature and low pressure Cu-Cu WoW bonding using ultra-thin Ti as passivation layer. We have proven that a thickness of 3 nm of Ti not only results in excellent bonding but also leads to a reduction in bonding temperature to 175° C [1]. Optimized Ti passivation gives us low temperature bonding [2], however Ti do get oxidized after prolonged exposer in air [3]. Therefore there is strong need for a passivation material which do not get oxidized for prolong time in an ambient air.

## 2 Experimental and Bonding Mechanism

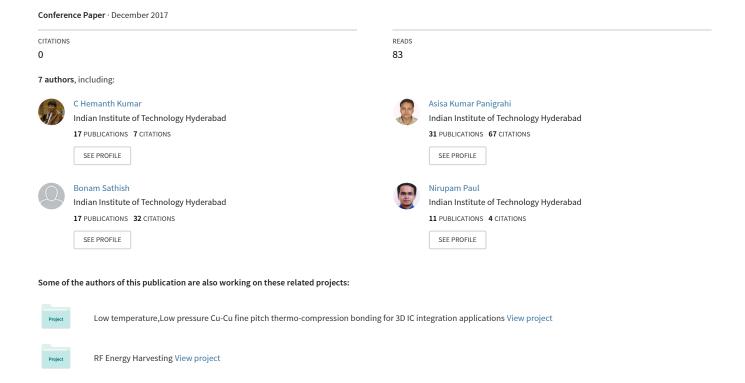

Cu has a lower activation energy at the interface [4] and Pd density is lower than that of pristine Cu (Pd has higher atomic radius of 1.69 A° than the Cu (1.41 A°)), hence during thermocompression cycle Cu atoms can easily diffuse through the Pd and forms a strong bond at the interface. Additionally, passivated Cu surface with ultra-thin Pd reflects more than 80% of <111> oriented Cu plane (Fig. 1 (a)) after annealing at 160°C for 50 mins under vacuum, which enhances the interdiffusion of Cu atoms at the interface up to 3 to 4 orders compared to other oriented Cu plane at the interface [16]. In this endeavor, Pd passivation thickness on Cu surface need to be optimized as it directly effects the bonding quality. Higher passivation thickness may either increase the contact resistance or it may hinder the interdiffusion of Cu atoms through Pd passivation layer. Also, lower passivation thickness may not passivate the Cu surface efficiently. Hence, Pd passivation thickness need to be optimized carefully in order to achieve low temperature and low pressure bonding.

In the whole experimental work, 4 inch P-type <100> prime Silicon wafers were used. Standard Piranha followed by BHF, RCA was used for cleaning wafers. Metal deposition was carried out on both the cleaned Si wafers in a sputtering chamber for 20 nm Ti (Cu diffusion barrier), 200 nm of Cu and 3 nm of optimized Pd in AJA International Inc. multi-source sputtering tool under room temperature. Then bonding process was carried out in AML alignment wafer bonder machine by keeping both the metal film deposited wafers face to face on the wafer chuck. After Nitrogen treatment, vacuum was created up to 1 E -5 mbar [5]. Then the wafers are being heated at a rate of 46 °C/min. Moment the temperature reaches 150 °C, a 4 bar pressure was applied for 50 mins. Thereafter, 2 hrs. duration is required to cool the wafers to room temperature. Then bonded sample was taken for different post bonding analysis.

## 3 Results and Discussion

#### 3.1 Pre-bonding Surface Analyses

The thickness of Pd layer plays an important role in achieving good and reliable bonding. This is because, higher film thickness might prevent interdiffusion of Cu and lower film thickness might not be able to prevent oxidation of Cu effectively nor can it reduce the surface roughness. In this endeavor, passivation thickness was optimized by varying Pd metal passivation on Cu surface by performing AFM studies at tapping mode to study the effect of surface roughness. The minimum RMS roughness obtained using ultra-thin Pd of 3 nm coated Cu sample was observed 0.97 nm (Fig. 1 (b)) which is very less compared to control Cu sample.

**Fig. 1:** (a) Diffraction pattern of Pd passivated Cu surface under similar thermocompression cycle, (b) Variation of Cu surface roughness with different Pd passivation thickness obtained from AFM tool.

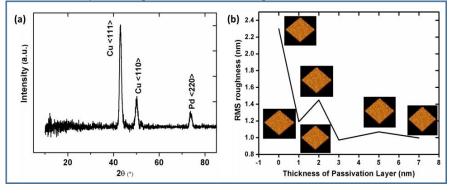

After determining the minimal surface roughness obtained on the Cu surface with 3 nm thick Pd passivation layer, next important task is to quantify the efficacy of the passivation layer under harsher environment conditions. To confirm the efficacy of Pd as a passivation layer, a Pd passivated Cu sample (with Pd thickness having 3 nm) and a control Cu sample (~200 nm thick) were heated continuously at 300 °C using hotplate. Then contact angel measurement was performed for both the samples periodically up to 24 hrs as shown in Fig. 2 (a). It is clearly evident from the figure that Pd passivated Cu surface contact angel remained almost unaltered even after continuous heating for 24 hours. But, control Cu is hydrophilic in nature. Also, one can easily visualize from Fig. 2 (a) that contact angle almost reaches 90° for the unpassivated Cu surface. This is a clear indication of Cu surface getting highly oxidized for the unpassivated sample. This confirms that Pd passivation prevents the formation of oxide film on the Pd passivated Cu sample.

**Fig. 2: (a)** Comparison study of contact angel measurement between control Cu sample and Cu surface passivated with various Pd passivation thickness, **(b)** Wafer level C-SAM imaging of Cu/Pd-Pd/Cu bonded structure.

#### 3.2 Post-bonding Analyses

To reaffirm the quality of bond interface and presence of any uneven voids at the interface, C-Mode Scanning Acoustic Microscopy (C-SAM) was performed on passivated bonded sample. C-SAM is a non-destructive interface analysis technique used to evaluate the bonding quality. It is basically equipped with a transducer (100 MHz), which transforms the sound pulses into electromagnetic pulses which are displayed as pixels with defined grey values. Inherent dark image confirm very good interface of Cu-Cu bonded structure with 3 nm Pd passivation layer as shown in Fig. 2 (b). Very sparse voids at the interface seen in the C-SAM image are attributed to contaminants or dust particles prior to Cu-Cu bonding.

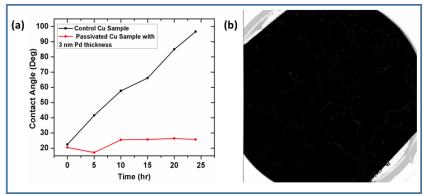

Furthermore, in order to qualify the bond strength, simple razor blade test, and mechanical shear tests were applied to the Cu/Pd-Pd/Cu bonded interface. Razor test was carried out to realize if penetration of blade is possible or not. A high quality bonded sample does not allow penetration of the blade at all. As per observation, razor blade could not penetrate through bonded samples at 150 °C and 4 bar pressure for Cu-Cu bonded structure with 3 nm Pd passivation. In addition, bonded structure was tested by shear test measurement using Instron Microtester by fixing one side of the

bonded wafer to the tool and other side of the bonded wafer was stressed by a load as shown in Fig. 3 (a). From Fig. 3 (b) one can easily realize that strength of the Cu-Cu interface is too high so that from portion of the fixed bonded wafer to the tool, Cu totally get pealed out from the Silicon. The bond strength is found to be 150 MPa, which clearly suggests that proposed bonding methodology is high quality and reliable.

Fig. 3: (a) Mechanical shear test mechanism, (b) Separated out bonded structure soon after mechanical shear test.

#### 4 Conclusion

We have successfully demonstrated a low temperature (150 °C) and low pressure (4 bar) Cu-Cu bonding using optimally chosen ultra-thin layer of Pd (3 nm). Efficacy of Cu surface passivation using ultra-thin Pd was thoroughly studied. This low temperature metal based passivation mechanism not only opens up windows for heterogeneous integration but also shows clear cut path to the visionary 3D IC integration to realty.

## References

- A. K. Panigrahi, S. Bonam, T. Ghosh, S. R. K. Vanjari, and S. G. Singh, "Low temperature, low pressure CMOS compatible Cu-Cu thermo-compression bonding with Ti passivation for 3D IC integration." In *Electronic Components and Technology Conference (ECTC)*, 2015 IEEE 65th, pp. 2205-2210. IEEE, 2015.

- A.K. Panigrahi, S. Bonam, T. Ghosh, S.G. Singh, and S.R.K. Vanjari, "Ultra-thin Ti passivation mediated breakthrough in high quality Cu-Cu bonding at low temperature and pressure," *Materials Letters*, vol.169, pp. 269-272, 2016.

- 3. M. C. Burrell, and N.R. Armstrong, "Oxides formed on polycrystalline titanium thin-film surfaces: rates of formation and composition of oxides formed at low and high O2 partial pressures," *Langmuir*, vol. 2, no. 1, pp. 30-36, 1986.

- E. S. Machlin, An Introduction to Aspects of Thermodynamics and Kinetics Relevant to Materials Science, Burlington, MA, USA: Elsevier, 248–252, 2007.

- A. K. Panigrahi, T.Ghosh, S. R. K.Vanjari, and S.G.Singh, "Oxidation resistive, CMOS compatible Copper based Alloy ultrathin films as a superior passivation mechanism for achieving 150°C Cu-Cu wafer on wafer thermocompression bonding," IEEE Transactions on Electron Devices, 64(3), pp.1239-1245, 2017.