# Algorithms for Power Aware Testing of Nanometer Digital ICs

A THESIS

submitted by

## A. SATYA TRINADH

for the award of the degree

of

### DOCTOR OF PHILOSOPHY

भारतीय प्रौद्योगिकी संस्थान हैदराबाद Indian Institute of Technology Hyderabad

## **DEPARTMENT OF COMPUTER SCIENCE AND**

## ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY HYDERABAD

Nov 2016

#### Declaration

I declare that this written submission represents my ideas in my own words, and where others' ideas or words have been included, I have adequately cited and referenced the original sources. I also declare that I have adhered to all principles of academic honesty and integrity and have not misrepresented or fabricated or falsified any idea/data/fact/source in my submission. I understand that any violation of the above will be a cause for disciplinary action by the Institute and can also evoke penal action from the sources that have thus not been properly cited, or from whom proper permission has not been taken when needed.

A-Satya Trindh

A. SATYA TRINADH

CSILPIOO

#### **Approval Sheet**

Acad-127 14843/21/5/2018

This thesis entitled Algorithms for Power Aware Testing of Nanometer Digital ICs by (A. Satya Trinadh) is approved for the degree of Doctor of Philosophy from IIT Hyderabad.

Prof. Anshul Kumar IIT Delhi Examiner M.V. Pandwar

Dr. M V Panduranga Rao IIT Hyderabad Internal Examiner

Sobhanbale

Dr. Ch Sobhan Babu IIT Hyderabad Adviser/Guide

Jar S

Dr. Shiv Govind Singh IIT Hyderabad Co-Adviser

V.C.V

Dr. V Chandrika Prakash IIT Hyderabad Chairman

#### ACKNOWLEDGEMENTS

I would like to express my sincere gratitude to my research advisors Dr. Ch. Sobhan Babu and Dr. Shiv Govind Singh for their continuous advice and encouragement throughout my research.

I would like to thank my doctoral committee members Dr. M.V. Panduranga Rao, Dr. Naveen Sivadasan and Dr. Asudeb Dutta for providing constructive criticism and encouragement during my doctoral committee meetings.

My sincere thanks to Prof. V. Kamakoti from IIT Madras for teaching me Digital Systems Testing, proving access to facilities in Reconfigurable Intelligent Systems Engineering (RISE) lab and helping me during struggling phase of my research.

I am grateful to Seetal Potluri from RISE Lab, IIT Madras for his care and precious friendship during my stay at IIT Madras. I am thankful to him for consistently helping me throughout my research and for the support to make this thesis possible.

I would like to thank my friend Valeti Nageswara Rao who helped me during my research work.

I offer my sincere thanks to all my research colleagues at Software Systems Research Lab (SSRL) Lab for all the help and cooperation.

Finally, I take this opportunity to express the profound gratitude from my deep heart to my beloved parents, brothers, wife and kids for their love, continuous encouragement and support.

This thesis is heartily dedicated to my parents who took the lead to heaven before the completion of this work.

### ABSTRACT

#### KEYWORDS: Digital system testing, At-speed testing, Capture power, Test Vector Ordering, X-filling

At-speed testing of deep-submicron digital very large scale integrated (VLSI) circuits has become mandatory to catch small delay defects. Now, due to continuous shrinking of complementary metal oxide semiconductor (CMOS) transistor feature size, power density grows geometrically with technology scaling. Additionally, power dissipation inside a digital circuit during the testing phase (for test vectors under all fault models (Potluri, 2015)) is several times higher than its power dissipation during the normal functional phase of operation. Due to this, the currents that flow in the power grid during the testing phase, are much higher than what the power grid is designed for (the functional phase of operation). As a result, during at-speed testing, the supply grid experiences unacceptable supply IR-drop, ultimately leading to delay failures during functional phase of operation of the chip, these failures are usually referred to false failures, and they reduce the yield of the chip, which is undesirable.

In nanometer regime, process parameter variations has become a major problem. Due to the variation in signalling delays caused by these variations, it is important to perform at-speed testing even for stuck faults, to reduce the test escapes (McCluskey and Tseng, 2000; Vorisek *et al.*, 2004). In this context, the problem of excessive peak power dissipation causing false failures, that was addressed previously in the context of at-speed transition fault testing (Saxena *et al.*, 2003; Devanathan *et al.*, 2007*a,b,c*), also becomes prominent in the context of at-speed testing of stuck faults (Maxwell *et al.*, 1996; McCluskey and Tseng, 2000; Vorisek *et al.*, 2000; Vorisek *et al.*, 2004; Prabhu and Abraham, 2012; Potluri, 2015; Potluri *et al.*, 2015). It is well known that excessive supply IR-drop during at-speed testing can be kept under control by minimizing switching activity during testing (Saxena *et al.*, 2003). There is a rich collection of techniques proposed in the past for reduction of peak switching activity during at-speed testing of transition/delay faults

in both combinational and sequential circuits. As far as at-speed testing of stuck faults are concerned, while there were some techniques proposed in the past for combinational circuits (Girard *et al.*, 1998; Dabholkar *et al.*, 1998), there are no techniques concerning the same for sequential circuits. *This thesis addresses this open problem*. We propose algorithms for minimization of peak switching activity during at-speed testing of stuck faults in sequential digital circuits under the combinational state preservation scan (CSP-scan) architecture (Potluri, 2015; Potluri *et al.*, 2015). First, we show that, under this CSP-scan architecture, when the test set is completely specified, the peak switching activity during testing can be minimized by solving the Bottleneck Traveling Salesman Problem (BTSP). This mapping of *peak test switching activity minimization problem* to *BTSP* is novel, and proposed for the first time in the literature.

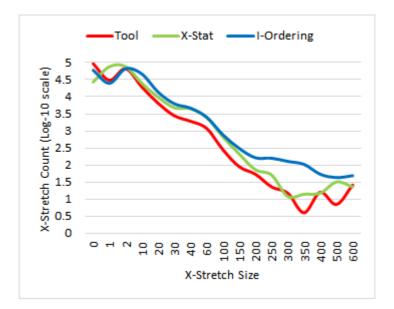

Usually, as circuit size increases, the percentage of don't cares in the test set increases. As a result, test vector ordering for any arbitrary filling of don't care bits is insufficient for producing effective reduction in switching activity during testing of large circuits. Since don't cares dominate the test sets for larger circuits, don't care filling plays a crucial role in reducing switching activity during testing. Taking this into consideration, we propose an algorithm, *XStat*, which is capable of performing test vector ordering while preserving don't care bits in the test vectors, following which, the don't cares are filled in an intelligent fashion for minimizing input switching activity, which effectively minimizes switching activity inside the circuit (Girard *et al.*, 1998). Through empirical validation on benchmark circuits, we show that *XStat* minimizes peak switching activity significantly, during testing.

Although *XStat* is a very powerful heuristic for minimizing peak input-switchingactivity, it will not guarantee optimality. To address this issue, we propose an algorithm that uses *Dynamic Programming* to calculate the lower bound for a given sequence of test vectors, and subsequently uses a *greedy strategy* for filling don't cares in this sequence to achieve this lower bound, thereby guaranteeing optimality. This algorithm, which we refer to as *DP-fill* in this thesis, provides the *globally optimal* solution for minimizing peak input-switching-activity and also is the best known in the literature for minimizing peak input-switching-activity during testing. The proof of optimality of *DP-fill* in minimizing peak input-switching-activity is also provided in this thesis.

# **TABLE OF CONTENTS**

| A  | CKNO | OWLEDGEMENTS                                                                 | i    |

|----|------|------------------------------------------------------------------------------|------|

| AI | BSTR | RACT                                                                         | ii   |

| LI | ST O | OF TABLES                                                                    | vii  |

| LI | ST O | <b>DF FIGURES</b>                                                            | viii |

| AJ | BBRF | EVIATIONS                                                                    | X    |

| N  | OTAT | TIONS                                                                        | xi   |

| 1  | Intr | oduction                                                                     | 1    |

|    | 1.1  | Power issues during at-speed testing                                         | 1    |

|    | 1.2  | Reduction of peak power during testing of combinational circuits             | 3    |

|    | 1.3  | Reduction of peak power during testing of sequential circuits                | 4    |

| 2  | Bac  | kground                                                                      | 7    |

|    | 2.1  | Related work in low power testing                                            | 8    |

|    | 2.2  | Motivation for at-speed stuck-at testing                                     | 9    |

|    | 2.3  | Design for Testability                                                       | 10   |

|    |      | 2.3.1 Enhanced Scan (ES) scheme                                              | 11   |

|    |      | 2.3.2 CSP-scan scheme                                                        | 12   |

| 3  |      | Efficient Test Vector Ordering Algorithm for Minimizing Peak tching Activity | 15   |

|    | 3.1  | PITMP and BTSP                                                               | 15   |

|    | 3.2  | Mapping of PITMP vs BTSP                                                     | 17   |

|    |      | 3.2.1 Mapping of PITMP to BTSP                                               | 18   |

|    |      | 3.2.2 Mapping of BTSP to PITMP                                               | 18   |

|   | 3.3  | Algori   | thm for BTSP                                                 | 19 |

|---|------|----------|--------------------------------------------------------------|----|

|   | 3.4  | Experi   | imental Results                                              | 22 |

|   |      | 3.4.1    | Experimental Setup                                           | 22 |

|   |      | 3.4.2    | Results                                                      | 23 |

|   | 3.5  | Summ     | ary                                                          | 33 |

| 4 | An ] | Efficien | t X-filling algorithm for Minimizing Peak Switching Activity | 37 |

|   | 4.1  | Peak I   | nput Toggle Minimization Problem (PITMP)                     | 38 |

|   | 4.2  | Balanc   | ced X-Filling (B-Fill) Algorithm                             | 38 |

|   |      | 4.2.1    | Motivation                                                   | 38 |

|   |      | 4.2.2    | Existing X-Filling Techniques                                | 39 |

|   |      | 4.2.3    | Algorithm Details                                            | 40 |

|   | 4.3  | Test C   | ube Ordering Algorithm                                       | 41 |

|   |      | 4.3.1    | The Need for an Efficient Test Cube Order                    | 43 |

|   |      | 4.3.2    | The X-Based Ordering Algorithm                               | 44 |

|   |      | 4.3.3    | Effectiveness of X-Based Ordering Algorithm                  | 44 |

|   | 4.4  | Integra  | ated Test Vector Ordering and X-filling Algorithm            | 47 |

|   | 4.5  | Experi   | imental Results                                              | 49 |

|   |      | 4.5.1    | Experimental Setup                                           | 49 |

|   | 4.6  | Summ     | ary                                                          | 51 |

| 5 | An   | Optima   | l X-Filling algorithm for Minimizing Peak Switching Activity | 55 |

|   | 5.1  | Peak I   | nput Toggle Minimization Problem (PITMP)                     | 55 |

|   | 5.2  | Bottle   | neck Coloring Problem (BCP)                                  | 56 |

|   |      | 5.2.1    | Problem Statement                                            | 56 |

|   |      | 5.2.2    | Dynamic Programming Algorithm to compute Lower-Bound         | 57 |

|   |      | 5.2.3    | Greedy Algorithm for Bottleneck Coloring Problem             | 57 |

|   |      | 5.2.4    | Proof of correctness                                         | 58 |

|   | 5.3  | Optim    | al X-Filling Algorithm                                       | 59 |

|   |      | 5.3.1    | Motivation                                                   | 59 |

|   |      | 5.3.2    | Algorithm Details                                            | 59 |

|   | 5.4  | Test V   | ector Ordering Algorithm                                     | 60 |

|   |     | 5.4.1    | Motivation                                         | 60 |

|---|-----|----------|----------------------------------------------------|----|

|   |     | 5.4.2    | Algorithm Details                                  | 60 |

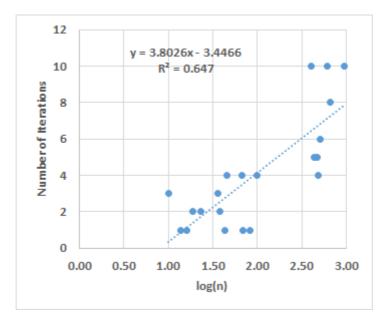

|   |     | 5.4.3    | Experimental Results                               | 61 |

|   | 5.5 | Bottler  | neck Minimization Algorithm                        | 61 |

|   | 5.6 | Experi   | mental Results                                     | 62 |

|   |     | 5.6.1    | Experimental Setup                                 | 62 |

|   |     | 5.6.2    | Results                                            | 62 |

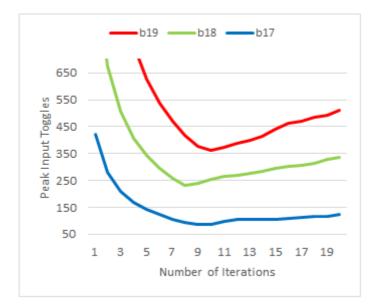

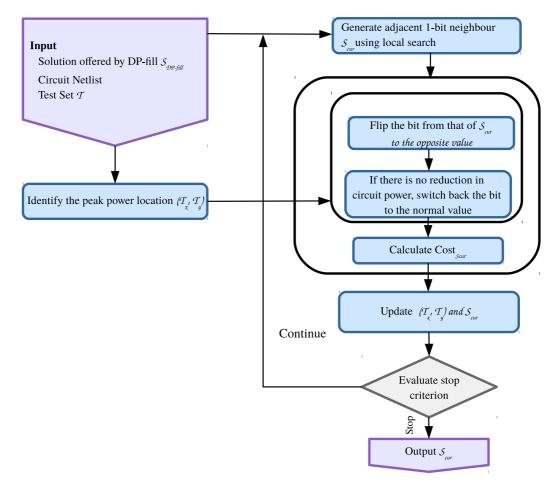

|   | 5.7 | Local S  | Search With Iterative 1-bit Neighbourhood          | 64 |

|   | 5.8 | Summ     | ary                                                | 76 |

| 6 | Con | clusions | 3                                                  | 77 |

|   | 6.1 | Test ve  | ector ordering for fully specified test sets       | 77 |

|   | 6.2 | Simult   | aneous test vector ordering and don't care filling | 78 |

|   | 6.3 | An opt   | imal algorithm for peak input switching activity   | 79 |

|   | 6.4 | Future   | Work                                               | 79 |

# LIST OF TABLES

| 2.1 | ITC'99 Benchmarks (X % : Average % of X-bits in test cubes)                | 14 |

|-----|----------------------------------------------------------------------------|----|

| 3.1 | ITC'99 Benchmarks                                                          | 28 |

| 3.2 | Edge cost : Primary input toggles per vector pair                          | 29 |

| 3.3 | Edge cost : Circuit total toggles per vector pair                          | 30 |

| 3.4 | Edge cost : Circuit total power (in $\mu$ W) per vector pair               | 31 |

| 3.5 | Impact of test vector ordering for different cost functions considered     | 32 |

| 3.6 | Peak power comparisons for different cost functions considered             | 34 |

| 3.7 | Average power comparisons for different cost functions considered .        | 35 |

| 4.1 | ITC'99 benchmarks (X % : Average % of X-bits in test cubes)                | 37 |

| 4.2 | Lookup table for X-filling                                                 | 40 |

| 4.3 | Peak input toggles : Tool-Ordering with different X-fillings               | 49 |

| 4.4 | Peak input toggles : BTSP-Ordering followed by different X-fillings        | 50 |

| 4.5 | Peak input toggles : X-Base-Ordering with different X-fillings             | 51 |

| 4.6 | Peak input toggles : Comparison of XStat-Method over existing meth-<br>ods | 52 |

| 4.7 | Peak circuit power : Comparison of XStat-Method over existing meth-<br>ods | 53 |

| 4.8 | Computation time in performing test vector ordering                        | 54 |

| 5.1 | ITC'99 benchmarks (X % : Average % of X-bits in test cubes)                | 68 |

| 5.2 | Peak input toggles : Tool-ordering with different X-fillings               | 69 |

| 5.3 | Peak input toggles : BTSP-Ordering followed by different X-fillings        | 70 |

| 5.4 | Peak input toggles : X-Base-Ordering with different X-fillings             | 71 |

| 5.5 | Peak input toggles : I-Ordering with different X-fillings                  | 72 |

| 5.6 | Peak input toggles : Comparison of DP-Method over existing methods         | 73 |

| 5.7 | Peak circuit power : Comparison of DP-Method over existing methods         | 74 |

| 5.8 | Additional savings using local search with 1-bit Neighbourhood             | 75 |

# LIST OF FIGURES

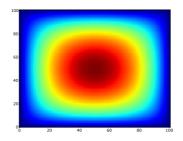

| 1.1 | Static IR-drop profile on a 100x100 power grid                                        | 3  |

|-----|---------------------------------------------------------------------------------------|----|

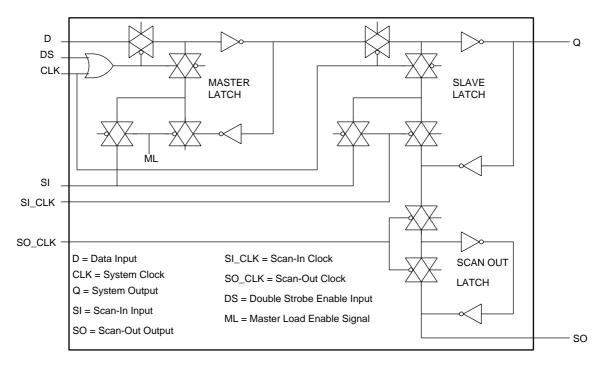

| 2.1 | Enhance Scan Flip-Flop proposed in (Dervisoglu and Stong, 1991) .                     | 11 |

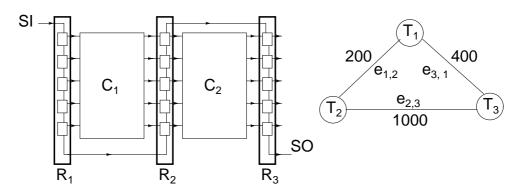

| 2.2 | Combinational State Preservation (CSP) proposed in (Potluri, 2015)                    | 12 |

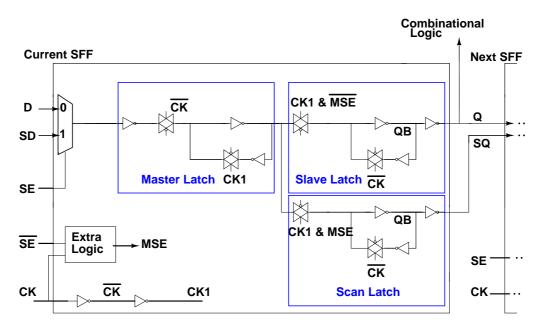

| 2.3 | Scan flip-flop that implements the CSP-scan scheme (Potluri, 2015)                    | 13 |

| 2.4 | Timing diagram for CSP-scan scheme (Potluri, 2015)                                    | 14 |

| 3.1 | An example of edge-weighted undirected complete graph, $G$                            | 16 |

| 3.2 | Bottleneck Hamiltonian Cycles (BHCs) in $G$                                           | 17 |

| 3.3 | Bottleneck Hamiltonian Cycle, Path in $G'$                                            | 18 |

| 3.4 | BBSS and NN in $G'$                                                                   | 22 |

| 4.1 | Motivation for Balanced-X-Filling (B-Fill)                                            | 40 |

| 4.2 | Don't care distribution in test cubes                                                 | 44 |

| 4.3 | Computing X-base metric, X-base $(TC_1, TC_2) = 5 \dots \dots$                        | 46 |

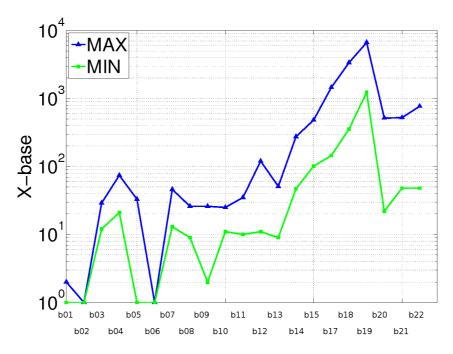

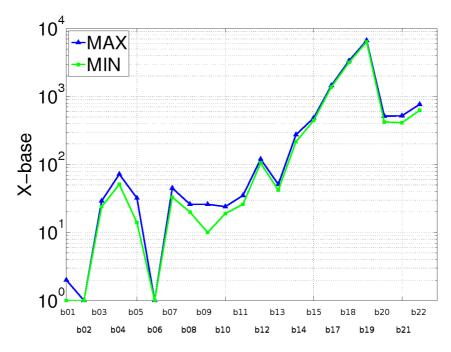

| 4.4 | Gap between MAX-X-BASE and MIN-X-BASE for test cube ordering given by commercial tool | 47 |

| 4.5 | Gap between MAX-X-BASE and MIN-X-BASE for X-based test cube ordering                  | 48 |

| 5.1 | Motivation for Optimum-X-Filling (O-Fill)                                             | 60 |

| 5.2 | Don't care-stretch analysis on b19                                                    | 61 |

| 5.3 | Bottleneck minimization algorithm iterations                                          | 62 |

| 5.4 | Bottleneck minimization algorithm iterations                                          | 63 |

| 5.5 | Local search technique with 1-bit neighbourhood                                       | 65 |

# List of Algorithms

| 1  | NNH Algorithm                              | 20 |

|----|--------------------------------------------|----|

| 2  | BBSSP Algorithm                            | 21 |

| 3  | BTSP Algorithm                             | 25 |

| 4  | Enhanced Lower Bound Algorithm             | 26 |

| 5  | BTSPP Algorithm                            | 27 |

| 6  | Balanced X-Fill (B-Fill) Algorithm         | 42 |

| 7  | X-Based Test Cube Ordering Algorithm       | 45 |

| 8  | Bottleneck Minimization Algorithm          | 48 |

| 9  | Algorithm for Computing Lower-Bound        | 57 |

| 10 | Algorithm for assigning color to intervals | 58 |

| 11 | Optimal X-Filling Algorithm                | 66 |

| 12 | Test Vector Ordering Algorithm             | 67 |

| 13 | Bottleneck Minimization Algorithm          | 67 |

# ABBREVIATIONS

| IITH  | Indian Institute of Technology, Hyderabad  |  |  |  |

|-------|--------------------------------------------|--|--|--|

| VLSI  | Very Large Scale Integration               |  |  |  |

| DFT   | Design For Testability                     |  |  |  |

| LOC   | Launch On Capture                          |  |  |  |

| LOS   | Launch On Shift                            |  |  |  |

| CSP   | Combinational State Preservation           |  |  |  |

| ES    | Enhanced Scan                              |  |  |  |

| TVO   | Test Vector Ordering                       |  |  |  |

| ATPG  | Automatic Test Pattern Generation          |  |  |  |

| PITMP | Peak Input Toggle Minimization Problem     |  |  |  |

| BTSP  | Bottleneck Traveling Salesman Problem      |  |  |  |

| BTSPP | Bottleneck Traveling Salesman Path Problem |  |  |  |

| BHC   | Bottleneck Hamiltonian Cycle               |  |  |  |

| BBSS  | Bottleneck Biconnected Spanning Subgraph   |  |  |  |

| NNH   | Nearest Neighbour Hood                     |  |  |  |

| LB    | Lower Bound                                |  |  |  |

| PIT   | Primary Input Toggles                      |  |  |  |

| CTT   | Circuit Total Toggles                      |  |  |  |

| СТР   | Circuit Total Power                        |  |  |  |

| DP    | Dynamic Programming                        |  |  |  |

| SA    | Simulated Annealing                        |  |  |  |

| ITC   | International Test Conference              |  |  |  |

| PI    | Primary Input                              |  |  |  |

| PPI   | Pseudo Primary Input                       |  |  |  |

| TV    | Test Vector                                |  |  |  |

| TC    | Test Cube                                  |  |  |  |

## NOTATIONS

| C            | Circuit                      |

|--------------|------------------------------|

| X            | Don't care                   |

| G            | Graph                        |

| V            | Vertices                     |

| E            | Edges                        |

| P            | Polynomial                   |

| NP           | Non-deterministic Polynomial |

| $\mu W$      | Micro Watt                   |

| %            | Percentage                   |

| 0            | Big-O                        |

| #            | Number of                    |

| $\pi$        | Order                        |

| $\epsilon$   | Approximation ratio          |

| [, ]         | Floor                        |

| [,]          | Ceil                         |

| $\leftarrow$ | Assignment                   |

| /*,*/        | Comment                      |

| Ø            | Empty set                    |

| $\infty$     | Infinite                     |

| $\delta$     | Delta                        |

| $\forall$    | For all                      |

| $\in$        | in                           |

| $\sum$       | sum                          |

## **CHAPTER 1**

#### Introduction

According to Dennard's scaling (Dennard *et al.*, 1974), power density should remain constant, even with increasing device densities. But exponential increase in subthreshold leakage with threshold voltage scaling caused leakage power to dominate total power consumption (Borkar, 1999). Due to this, threshold voltage scaling and Dennard's scaling came to an end below 100nm, causing power density to rise exponentially with successive technology generations. Today, aggravated power densities and hot spots have become one of the most important concerns in the nanoscale circuit design. Additionally power dissipation for test vectors is several times higher than that of functional vectors (Gerstendorfer and Wunderlich, 1999). Next, we shall see the issues with these elevated levels of power dissipation during testing.

### **1.1** Power issues during at-speed testing

The problems concerning test power are two fold. The *first problem* is one of high average test power, which increases thermal stress (Huang, 2007; Yao *et al.*, 2011) on the chip during testing, thereby decreasing its reliability (Saxena *et al.*, 2001; Girard, 2002). In worst cases, the chip can burn on the tester, thereby leading to destructive testing. *The second problem* is that of high peak power during testing. Since power grid is designed for functional vectors, the excessive power dissipation during test vector application can cause excessive IR-drop (Wen *et al.*, 2007; Devanathan *et al.*, 2007*b*), causing timing failures. Since such elevated power levels are not observed during regular operation, such timing failures are categorized as false failures. Since these failures don't occur during the chip's normal functional mode of operation, this problem is also popularly known as the *over testing* problem. This kind of over testing can drastically reduce the fabrication yield, ultimately causing a huge financial loss for the semiconductor manufacturer. Now, at-speed scan based testing is crucial to catch small delay defects that occur during the fabrication of high performance digital chips (Ahmed

*et al.*, 2006*a*; Yilmaz *et al.*, 2008*b*,*a*; Peng *et al.*, 2010; Goel *et al.*, 2010; Yilmaz *et al.*, 2010, 2011; Tehranipoor *et al.*, 2011; Peng *et al.*, 2013; Bao *et al.*, 2013*a*,*b*). These small delay defects can manifest themselves as delay faults, transition faults or stuck-at faults (Chakraborty and Agrawal, 1995*a*,*b*). Since launch to capture clock cycle is very small during at-speed testing, capture is performed when dynamic IR-drop is very high. This causes excessive gate delays on the critical path (Saxena *et al.*, 2003), thus making the over testing problem even more pronounced during at-speed testing. Hence, peak power reduction during at-speed testing is an important problem in the broad area of VLSI testing.

Launch-Off-Capture (LOC), Launch-Off-Shift (LOS) and Enhanced Scan (ES) are the available design-for-testability (DFT) schemes in the literature for the purpose of atspeed testing. Taking physical design overheads and limitations into account, LOC and LOS are the two prevalently used schemes for this purpose. LOS achieves higher fault coverage while consuming lesser test time over LOC scheme, but dissipates higher peak power during the capture phase of the at-speed test (Wu *et al.*, 2011). This excessive peak power in LOS scheme, leads to high *IR-drop* on the power grid, more than what the power grid is designed to handle. This excessive *IR-drop* on the power grid, during capture phase of LOS scheme leads to false delay failures, thereby leading to significant yield reduction that is unwarranted.

This thesis proposes efficient solutions for minimizing peak switching activity during testing, to keep *IR-drop* under control during the same. In static mode, the *IR-drop* increases as the nodes on the power grid get farther from the supply voltage source as shown in Figure 1.1. This figure shows the static supply voltage map for a 100x100 grid with voltage sources at all the nodes on the periphery. The power grid is a rectangular mesh network with each node in the network having current sink of 1 $\mu$ A, simulated using SPICE. Although in practice, all the periphery nodes will not have supply voltage sources, this map is shown to illustrate the idea that the IR-drop increases as the nodes go farther from the supply pins. As already explained during at-speed testing *IR-drop* is strongly correlated to the toggle rates inside the digital circuit during the testing process (Saxena *et al.*, 2003). We thus focus on minimizing peak switching activity as a means to keep *IR-drop* under control during the testing process.

Figure 1.1: Static IR-drop profile on a 100x100 power grid

There has been work in the past for minimizing peak switching activity during testing of combinational circuits (Dabholkar *et al.*, 1998; Girard *et al.*, 1998). However, most of the current high-performance designs are highly pipelined and hence are inherently sequential in nature. These sequential circuits use scan based methodology for the purpose of testing. Due to the disturbance caused in the combinational logic in the scan-shift phase, the peak switching activity reduction techniques proposed in the past for combinational circuits, are not directly applicable to sequential circuits. However, it should be noted that under the CSP-scan architecture (Potluri, 2015; Potluri *et al.*, 2015), many of the algorithms for peak switching activity reduction during testing of combinational circuits. To motivate, we next discuss the techniques proposed in the past for peak switching activity reduction during testing of combinational circuits.

# **1.2 Reduction of peak power during testing of combinational circuits**

Power dissipation in digital Complementary Metal Oxide Semiconductor (CMOS) circuits has two components, namely *static power* and *dynamic power*. Among the two, dynamic power is the major source of power dissipation while the circuit is in operation. Typically, a major portion of a circuit is kept active during testing. This is done to ensure that the total test time spent in testing a chip is reduced i.e., higher fault sampling per test vector. Therefore, dynamic power is the major contributor to power dissipation during testing of a digital chip. The dynamic power dissipation occurs at a node when it switches from  $0 \rightarrow 1$  or  $1 \rightarrow 0$ , and is directly proportional to the toggle count inside the combinational circuit. Additionally, since interconnect dimensions does not scale the same way as transistor dimensions, interconnect contributes majorly to dynamic power dissipation in today's nanometer CMOS circuits (Magen *et al.*, 2004; Qiu *et al.*, 2008; Potluri *et al.*, 2012). The problems with interconnect scaling further aggravate the timing/power issues during testing, so much, so that there were even techniques proposed on how to perform test vector selection based on interconnect and layout considerations (Yilmaz *et al.*, 2008*a*, 2010). The interconnect scaling asserts itself in another way, on the supply routing interconnects of the power-grid. The inductive effects on the power-grid that were negligible in previous technologies begin to manifest and dominate the *IR-drop* on the power-grid in the sub-100*nm* technologies (Pant, 2008; Pant *et al.*, 2010). Thus, the increased levels of dynamic power dissipation inside the circuit, produces heavy currents to traverse along the power-grid, creating dynamic inductive drops, which further aggravate the *supply IR-drop* during testing, that was discussed previously.

In (Girard *et al.*, 1998; Dabholkar *et al.*, 1998; Dabholkar and Chakravarty, 1994; Kavousianos *et al.*, 2004; Kurian *et al.*, 2009; Kumar *et al.*, 2010), it was shown that average switching activity during testing of combinational circuits can be reduced by ordering the test vectors as an instance of the Hamiltonian path problem, which is NP-hard. However, this mapping is restricted for minimization of average switching activity, and currently there is no mapping available for minimization of peak switching activity during testing through test vector ordering. For the first time in literature, this thesis proposes a theoretical mapping for peak test switching activity minimization through test vector ordering. The provided mapping is also extended to sequential circuits, which is described in detail in the next section.

# **1.3 Reduction of peak power during testing of sequen**tial circuits

Today, the scan architecture (Williams and Angell, 1973; Eichelberger, 1974; Eichelberger and Williams, 1977) is used as the de-facto standard for testing sequential circuits. This scheme converts a sequential circuit to a combinational circuit, for the pur-

pose of generating test vectors under the single-stuck-fault (SSF) model. As a result, the rich literature available for test generation (Funatsu *et al.*, 1975; Liaw *et al.*, 1980; Abramovici *et al.*, 1994; Malaiya and Narayanaswamy, 1983; Savir and McAnney, 1988; Schulz *et al.*, 1988; Glover and Mercer, 1988; Reddy *et al.*, 1992; McCluskey and Tseng, 2000; Lin *et al.*, 2001; Liu, 2004; Venkataraman *et al.*, 2004; Ahmed *et al.*, 2006*b*; Miyase and Kajihara, 2006; Bao *et al.*, 2013*a*) and fault simulation (Abramovici *et al.*, 1983; Waicukauski *et al.*, 1986; Takahashi *et al.*, 2006; Chakraborty and Agrawal, 1995*b*; Singh *et al.*, 2006; Bosio *et al.*, 2010) for combinational circuits, can be reused for sequential circuits. In the deep sub-micron CMOS technologies, at-speed testing is necessary to detect small delay defects. Enhanced Scan (ES), Launch on Capture (LOC) and Launch on Shift (LOS) are the currently existing techniques for at-speed testing (Liu, 2004).

In the presence of path delays that are comparable to the clock interval, delayed signal transitions or timing hazards influence the detection of defects. Due to the these variations in signalling delays, it is important to perform at-speed testing even for stuck faults, to reduce the test escapes (McCluskey and Tseng, 2000; Vorisek et al., 2004). It was shown in the past that under the ES architecture, stuck-at vectors can be reused for testing for transition faults (Liu, 2004), with *improvement* in transition fault coverage. But, the implementation of enhanced scan architecture is costly, due to the requirement of multiple clocks (Glover and Mercer, 1988; Dervisoglu and Stong, 1991), which is not feasible in today's designs where routing a single clock, is itself a formidable challenge. In addition to that, test vector ordering is ineffective for reducing peak test power in sequential circuits in standard LOS, LOC and enhanced scan architectures (Potluri, 2015). To address this issue, recently, CSP-scan architecture (Potluri et al., 2015) was proposed, which uses principles of asynchronous circuit design (Sparso and Furber, 2001), to preserve the state of the combinational logic both during scan-shift and capture cycles, thus making test vector ordering effective in reducing peak test power during at-speed testing of stuck faults as well as transition faults in sequential circuits. We assume that this architecture is in place, and propose efficient algorithms for test vector ordering and don't care filling. The following are the contributions of this thesis:

1. We show that given a fully specified test set, optimal test vector ordering problem under the CSP-scan architecture, maps to the Bottleneck Traveling Salesman Problem (BTSP) problem, which is NP-hard. We solve the optimal test vector ordering problem for all of the ITC circuits by using an efficient BTSP heuristic. Interestingly, the solution obtained in each of the benchmark circuits is globally optimal. The mapping, algorithm, experimentation results and the verification for global optimality of the solutions obtained is given in chapter 3.

- 2. The test sets are dominated by don't care bits for large circuits, making don't care filling very important for minimizing test power. This increases the hardness of the peak power minimization engine. Keeping this in mind, we propose an efficient heuristic (*XStat*) for test vector ordering and don't care filling in an integrated fashion, that produces solutions which reduce test power significantly, while taking very little time in arriving at the solutions. The details of the proposed heuristic and experimentation results are explained in chapter 4.

- 3. While *XStat* is an efficient heuristic for reducing input switching activity, thereby reducing circuit switching activity, it does not guarantee optimality. To address this issue, we show that given a test vector order, don't cares can be filled in an optimal way using *dynamic programming* so as to minimize input switching activity. The details of this algorithm, its proof of optimality and its improvements over *XStat* are explained in detail in chapter 5.

Under CSP-scan architecture, it is sufficient to validate the proposed algorithms for stuck fault vectors as the transition fault vectors as well as delay fault vectors can be derived from the stuck fault vectors using the technique proposed in (Liu, 2004). Thus, the algorithms proposed in this thesis are generic, in the sense that they are applicable to at-speed testing of faults under all of the aforementioned fault models. The rest of the thesis is organized into 5 chapters. The next chapter gives a background of the low power testing research area and the different techniques proposed in the past to address the low power testing problem. This chapter explains the techniques proposed in the past, at different levels of the VLSI flow, and sets the stage for explaining our contributions. Chapters 3, 4 and 5 explain our contributions. Chapter 6 concludes this thesis.

## **CHAPTER 2**

### Background

With technology scaling, the process complexity has increased exponentially. This huge increase in the process complexity, also led to a proportionate increase in manufacturing defect rates. Additionally, the thrust for high-speed devices has made designers focus on high-speed designs. In these high speed designs, the number of gates between two pipelines stages has reduced drastically. As a result, these defects often manifest themselves as small delay defects (Ahmed *et al.*, 2006b; Yilmaz *et al.*, 2008*b*,*a*; Goel *et al.*, 2010; Yilmaz *et al.*, 2010, 2011; Bao *et al.*, 2013*b*) in these high-speed designs. In the presence of path delays that are comparable to the clock interval, delayed signal transitions or timing hazards influence the detection of defects. Due to the these variations in signalling delays, it is important to perform at-speed testing even for stuck faults, to reduce the test escapes (McCluskey and Tseng, 2000; Vorisek *et al.*, 2004). However, with increase in test speed, peak power dissipation during at-speed stuck-at testing also increases proportionately. This thesis addresses this problem of peak power minimization during at-speed stuck-at testing.

This chapter is divided into three sections, and this sets the background necessary to understand the proposed algorithms for low power at-speed stuck-at testing. The first section explains the related work in the broad area of low power testing. The second section motivates why at-speed stuck-at testing is important, with an example. The third section explains the design-for-testability (DFT) architecture, in the presence of which, the proposed algorithms are effective in reducing the peak power dissipation during atspeed stuck-at testing. Next, we begin with the first section on prior work related to low power testing.

#### 2.1 Related work in low power testing

There have been several techniques proposed in the past for minimizing peak test power. These techniques can be broadly categorized into circuit level (Gerstendorfer and Wunderlich, 1999; Parimi and Sun, 2004; Bhunia *et al.*, 2005*a*; Devanathan *et al.*, 2007*c*), gate level (Girard *et al.*, 1999; Lee *et al.*, 2000; Almukhaizim and Sinanoglu, 2008; Lin and Rajski, 2008) and system level (Girard *et al.*, 1998; Dabholkar *et al.*, 1998; Sankar-alingam *et al.*, 2000; Sankaralingam and Touba, 2002; Devanathan *et al.*, 2007*b*; Yao *et al.*, 2011) techniques.

Circuit level techniques include supply gating (Bhunia *et al.*, 2005*a*), scan flip-flop redesign (Gerstendorfer and Wunderlich, 1999; Parimi and Sun, 2004; Xu and Singh, 2007; Ganesan and Khatri, 2008; Mishra *et al.*, 2010), supply voltage scaling (Devanathan *et al.*, 2007*c*) and circuit partitioning (Girard *et al.*, 1999; Almukhaizim and Sinanoglu, 2008). Gate level techniques include clock gating (Lee *et al.*, 2000), scan cell output gating (Lin and Rajski, 2008), and low power scan chain synthesis (Lee *et al.*, 2000; Bonhomme *et al.*, 2002; Bhattacharya, 2003; Bonhomme *et al.*, 2004). System level techniques include low power test vector generation (Devanathan *et al.*, 2007*b*), test compaction (Sankaralingam *et al.*, 2000; Sankaralingam and Touba, 2002), power aware test scheduling (Yao *et al.*, 2011), test vector ordering (Girard *et al.*, 1998; Dabholkar *et al.*, 1998) and X-filling (Devanathan *et al.*, 2007*b*).

Among these various possibilities, one should choose such a test strategy that minimizes peak power dissipation during testing and at the same time introduces very minimal area, timing and power overheads on the design in its normal functional mode of operation. Thus, system level techniques are most attractive as such techniques do not modify the design at all. This thesis focuses on such system level techniques for minimizing the peak power during at-speed testing of sequential circuits. Low power test vector generation is attractive as it reduces test power without modifying the design. However, due to the hard nature of the test generation and test set compaction problems, adding further constraints would increase the effort of the automatic test vector generation (ATPG) engine, thereby increasing the design cycle of the product. As this is not attractive, we focus on system level techniques that reduce test power significantly, with little increase in design time. In particular we focus on Test cube ordering and don't care filling. For combinational circuits, capture power is dependent on application of a pair of test vectors- the previous test vector followed by the current test vector. In (Girard *et al.*, 1998) it was shown how test vector ordering for average capture power minimization problem maps to the well known Least Cost Hamiltonian Path Problem which is NP-Hard. In the same paper, a 2-approximation algorithm for TSP was used to achieve reasonably good solutions. In this thesis for both combinational and sequential circuits, it was shown how test vector ordering for peak capture power minimization maps to Bottleneck Hamiltonian Path Problem, which is also NP-Hard. Further details of our contributions will be explained in furture chapters of this thesis.

#### 2.2 Motivation for at-speed stuck-at testing

The real defect is a short or an open between two nodes inside a gate. However, a defect can manifest itself as a stuck-at 0 or stuck-at 1 at the output of a gate. Apart from a defect manifesting itself as stuck-at 0 or stuck-at 1 at the output of a gate, it also changes the delay of the gate. Sometimes, a defect changes the truth table of a gate, which may not be exactly stuck-at 0 or stuck-at 1 behavior. However, they will be usually be caught by the stuck-at tests (McCluskey and Tseng, 2000). In fact, it was shown practically using manufacturing data, that at-speed stuck-at testing can greatly reduce the test escapes (McCluskey and Tseng, 2000; Vorisek *et al.*, 2004). *This motivates the need for at-speed application of stuck-at tests, to reduce the number of test escapes.*. This is especially true in today's chips which are fabricated in deep-submicron technologies, that contain many small delay defects (Ahmed *et al.*, 2006*b*; Yilmaz *et al.*, 2008*b*,*a*; Goel *et al.*, 2010; Yilmaz *et al.*, 2010, 2011; Bao *et al.*, 2013*b*). Now, during at-speed stuck-at testing, if peak power is high, then voltage drops on the power grid is also high, thereby causing excessive delays on gates, leading to the following two scenarios:

1. **good chip:** the response maybe delayed, and since we are capturing at-speed, we observe faulty response, and discard the chip, although it works well in the functional mode of operation (when the excessive delay on gates won't occur); or

2. **defective chip:** the effect of stuck fault maybe masked by an excessive delay of a gate caused by high peak power, which is another type of test escape (Chakraborty and Agrawal, 1995*a,b*). This fault can be caught using slow-speed stuck-at testing. However, this additional phase of slow-speed stuck-at testing, as the name indicates, is slow, and hence adds significantly to the test time in modern system-on-chips (SoCs), which are very complex. Now, if we reduce the peak power during the at-speed stuck-at testing, such delay effects on stuck-at testing (Chakraborty and Agrawal, 1995*a,b*) can be avoided, thereby reducing the test escapes during at-speed stuck-at testing, and hence an additional phase of slow-speed stuck-at testing can be avoided.

Thus, the advantages of minimizing peak power dissipation during at-speed testing are two-fold:

- 1. we can avoid a good chip being categorized as defective, which is the problem of *false negatives*, that impacts the yield of a product and a loss to the manufacturer; and more importantly

- 2. we can avoid a defective chip being categorized as good, which is the problem of *false positives*, that impacts the trust of the customers on the manufacturer, which leads to customer/business loss to manufacturer, finally ending in a financial loss to the manufacturer.

This motivates the need to minimize peak power dissipation during at-speed stuckat testing. Having motivated this, next we shall see the design for testability techniques existing in the literature, for at-speed testing and the appropriate technique amongst them for the problem under consideration.

### 2.3 Design for Testability

We focus on ordering the test vectors and selectively filling the don't care (X) bits in the test cubes to minimize peak test power, under the CSP-scan scheme. Before understanding the CSP-scan scheme, it will be useful to understand enhanced scan, the physical design and other limitations posed by this scheme and how the CSP-scan addresses these challenges, yet preserves the properties of enhanced scan. So, next we shall briefly discuss about enhanced scan.

Figure 2.1: Enhance Scan Flip-Flop proposed in (Dervisoglu and Stong, 1991)

#### 2.3.1 Enhanced Scan (ES) scheme

Originally, enhanced scan architecture was proposed in (Dervisoglu and Stong, 1991) for arbitrary two-vector application for at-speed testing of sequential circuits. The circuit schematic of this enhanced scan flip-flop is shown in Figure 2.1. From this schematic, it is clear that to implement this scheme, multiple other clocks ( $SI_CLK$ ,  $SO_CLK$ ) are required apart from the system clock (CLK). In today's highly complex chips, routing a single clock itself poses several key challenges like clock-skew, common-path pessimism removal etc. Keeping this in mind, it is beyond question to accept such an implementation, which needs system level routing of more than one clock signal.

Several new implementations of enhanced scan scheme were proposed recently (Datta *et al.*, 2004; Bhunia *et al.*, 2005*b*), to avoid the multiple-clock routing problem and minimize the physical design overhead. However, all of these techniques are meant for arbitrary two-vector application, in which (1) At first, the first vector is scanned in, (2) following which, the first vector is launched into the combinational logic; (3) then, second vector is scanned in, (4) following which, the second vector is launched into the combinational logic; and finally (5) the response is captured.

Figure 2.2: Combinational State Preservation (CSP) proposed in (Potluri, 2015)

Hence, it should be clear that the ES scheme is not suitable for test vector ordering, where, after launching each test vector into the combinational logic, the response is also captured. The response thereby captured also disturbs the state of the combinational logic. Thus, the ES scheme preserves the state of combinational logic only during scanshift and is unable to preserve the state of the combinational logic during the capture cycle. Recently, to address this issue, the combinational state preservation (CSP) scan scheme is proposed, that preserves the state of combinational logic during both scanshift and capture cycles. The next section explains the CSP-scan scheme in detail.

#### 2.3.2 CSP-scan scheme

The CSP-scan architecture is proposed in (Potluri, 2015) for the purpose of preserving combinational logic states during scan-shift as well as capture phases of LOS based atspeed scan testing. Figure 2.2 shows how the combinational logic states are so preserved that the sequential circuit can practically be treated as combinational circuit, and we can perform test vector ordering for minimizing peak switching activity.

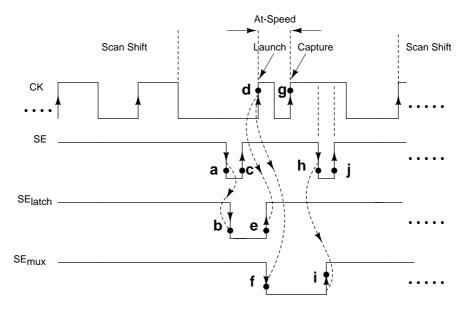

The scan flip-flop that implements the CSP-scan scheme is shown in Figure 2.3. The timing diagram corresponding to the CSP-scan scheme is shown in Figure 2.4. It can be seen that the  $SE_{latch}$  is low only during launch, and is high both during scan-shift and capture cycles, thus ensuring combinational state preservation between successive test vectors. It should be noted that, satisfaction of CSP makes test vector ordering effective in reducing peak power during LOS based at-speed testing of sequential circuits (Potluri, 2015).

Figure 2.3: Scan flip-flop that implements the CSP-scan scheme (Potluri, 2015)

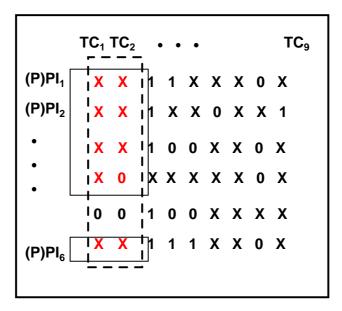

In this thesis, we focus on peak switching activity minimization during at-speed stuck-at testing. We assume that CSP-scan architecture is already in place and propose algorithms for the same. Additionally, the ATPG tool will give us the option to identify the don't care bits that can be replaced with 0 or 1, without loss in fault coverage (Miyase and Kajihara, 2006). Interestingly, the percentage of don't care bits is 67.8% on an average in the ITC circuits shown in Table 2.1. Since the majority of the bits in these sequential circuits are don't cares, don't care filling plays a major role in minimizing peak power during at-speed testing of sequential circuits. This thesis addresses the test vector ordering problem, the simultaneous vector ordering and don't care filling heuristic, and an optimal algorithm for don't care filling for a given test vector ordering. Chapters 3, 4 and 5 discuss these contributions in elaborate detail. The next chapter describes our first contribution.

Figure 2.4: Timing diagram for CSP-scan scheme (Potluri, 2015)

| Benchmark | # PIs | # Gates | # Test Cubes | X %  |

|-----------|-------|---------|--------------|------|

| b04       | 77    | 615     | 67           | 64.4 |

| b05       | 35    | 608     | 69           | 36.8 |

| b06       | 5     | 60      | 16           | 12.5 |

| b07       | 50    | 431     | 46           | 58.6 |

| b08       | 30    | 196     | 38           | 60.4 |

| b10       | 28    | 217     | 43           | 58.7 |

| b11       | 38    | 574     | 83           | 64.1 |

| b12       | 126   | 1.6K    | 100          | 76.9 |

| b13       | 53    | 596     | 36           | 65.4 |

| b14       | 275   | 5.4K    | 511          | 77.9 |

| b15       | 485   | 8.7K    | 405          | 87.8 |

| b17       | 1452  | 27.99K  | 618          | 89.9 |

| b18       | 3357  | 75.8K   | 666          | 86.9 |

| b19       | 6666  | 146.5K  | 953          | 89.8 |

| b20       | 522   | 9.4K    | 476          | 75.3 |

| b21       | 522   | 9.4K    | 479          | 73.2 |

| b22       | 767   | 13.4K   | 435          | 74.1 |

Table 2.1: ITC'99 Benchmarks (X % : Average % of X-bits in test cubes)

#### **CHAPTER 3**

# An Efficient Test Vector Ordering Algorithm for Minimizing Peak Switching Activity

As already explained in the previous chapter, under the CSP-scan architecture, the state of the combinational logic is preserved between application of successive test vectors. As a result, test vector ordering influences the peak switching activity during testing. In this chapter, we show that given a fully specified test set, the problem of optimal test vector ordering under the CSP-scan architecture (Potluri *et al.*, 2015), maps to the Bottleneck Traveling Salesman Problem (BTSP), which is NP-hard. We solve the test vector ordering problem by using an efficient BTSP heuristic (Larusic *et al.*, 2012). Interestingly, the solution obtained for all the benchmark circuits, is globally optimal.

Next, we define the Peak Input Toggle Minimization Problem (PITMP) and Bottleneck Traveling Salesman Problem (BTSP) respectively, and how one maps to the other. Section 3.3 explains the BTSP heuristic and section 3.4 provides the results obtained by implementing the proposed heuristic and experimenting it on benchmark circuits.

#### **3.1 PITMP and BTSP**

In this section, we shall see the definitions of the Peak Input Toggle Minimization Problem (PITMP) and Bottleneck Traveling Salesman Problem (BTSP) respectively, and how both of them map to each other.

**PITMP Definition:** Given a combinational circuit C, and a set of test vectors  $T = \{T_1 \dots T_k\}$ , the problem is to find an ordering  $\pi$  of these test vectors such that the  $max\{Hd \ (T_{\pi_1}, \ T_{\pi_2}), Hd \ (T_{\pi_2}, \ T_{\pi_3}), \dots Hd \ (T_{\pi_{k-1}}, \ T_{\pi_k})\}$  is *minimized*, where  $Hd \ (T_{\pi_i}, \ T_{\pi_{i+1}})$  is the *Hamming distance* between test vectors  $T_{\pi_i}$  and  $T_{\pi_{i+1}}$ .

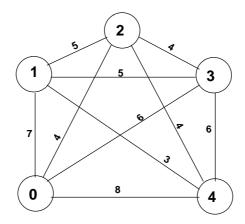

**BTSP Definition:** Given an edge-weighted undirected complete graph G, the problem is to find an *Hamiltonian cycle* in G, such that the *largest edge cost in this cy*-

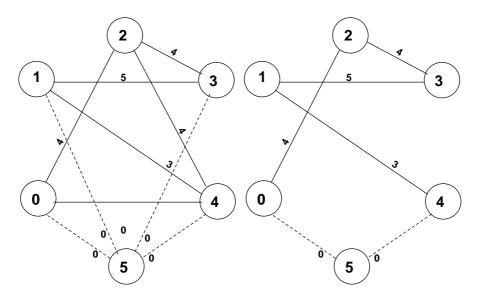

Figure 3.1: An example of edge-weighted undirected complete graph, G

*cle is minimized* (Garey and Johnson, 1990) (which is the Bottleneck Hamiltonian cycle). Figure 3.1 shows an example edge-weighted undirected complete graph G. Figures 3.2(a) and 3.2(b) show the Bottleneck Hamiltonian cycles (BHCs) in the complete graph (G) shown in Figure 3.1. In this specific example, there are two BHCs inside G. Thus, this example illustrates that the complete graph G, in general, can contain one or more BHCs. It depends on the distribution of weights on the edges of G. Now, we are interested in the peak switching activity, which is the largest edge-weight in the BHC (which will be explained later in the next section). Keeping in this mind, and the fact that the largest edge-weight in all the BHCs are equal, it is straightforward to see that all of the BHCs are equivalent, for the problem under consideration. This will become clearer as we go to the next section. Next, to take the discussion further, we will discuss the *bottleneck traveling salesman path problem*.

The BTSP is NP-Hard (Garey and Johnson, 1990). Next, we shall define the *Bottle*neck Traveling Salesman Path Problem and prove that it is equivalent to BTSP.

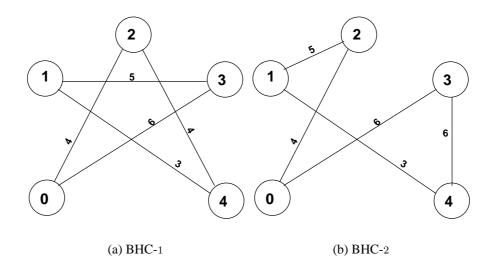

#### **Bottleneck Traveling Salesman Path Problem (BTSPP):**

Given an edge-weighted undirected complete graph G, the Bottleneck Traveling Salesman Path Problem (BTSPP) is to find an Hamiltonian path in G, such that the largest edge cost in this path is minimized. The BTSPP can be reduced to the BTSP, by adding a vertex to G, and connecting the same to all other vertices of G through edges with weight zero. Note that, after solving the BTSP on the modified graph, and removing the newly added vertex from the cycle thus computed, gives a bottleneck traveling salesman path in G.

Figure 3.2: Bottleneck Hamiltonian Cycles (BHCs) in G

It is interesting to note that, unless P = NP, there does not exist a polynomial time  $\epsilon$ -approximation algorithm for BTSP for any  $\epsilon > 0$  (Doroshko and Sarvanov, 1981; Parker and Rardin, 1984; Sarvanov, 1995). Several heuristics were reported in the literature for the BTSP problem, for example (Ramakrishnan *et al.*, 2009; Manku, 1996; Larusic *et al.*, 2012).

Next, we proceed towards showing that the PITMP can be reduced to BTSP. In this context, we define the *Hamming distance*(*Hd*) between test vectors  $T_i, T_j$  is defined as the number of positions in which ( $T_i=0$  and  $T_j=1$ ) or ( $T_i=1$  and  $T_j=0$ ). We denote this by  $Hd(T_i, T_j)$ . The proof of reduction is shown in the next section.

## 3.2 Mapping of PITMP vs BTSP

In this section we show that PITMP is NP-Hard. We do this by two way reduction between these two problems. Since BTSP is known to be NP-hard due to reduction PITMP is also NP-hard. Next we see the first reduction.

Figure 3.3: Bottleneck Hamiltonian Cycle, Path in G'

#### **3.2.1 Mapping of PITMP to BTSP**

In this section, we prove that the PITMP can be reduced to BTSP. To begin with, we construct a graph TVG = (V, E) as follows:

- Let V = {v<sub>1</sub>...v<sub>k</sub>} be a set of vertices such that vertex v<sub>i</sub> corresponds to test vector T<sub>i</sub>, for 1 ≤ i ≤ k.

- Place an edge  $(v_i, v_j)$  between vertices  $v_i, v_j$  with cost  $c_{i,j}$ , where  $c_{ij} = Hd(T_i, T_j), \forall i, j, 1 \le i < j \le k$ .

- Add a new vertex  $v_{k+1}$  to G and place edge between  $v_{k+1}$  and  $v_i, \forall 1 \le i \le k$ , with a cost  $c_{k+1,i} = 0, \forall 1 \le i \le k$ .

In the graph so constructed, let C be an optimal BTSP solution. Let P be a path obtained by removing vertex  $v_{k+1}$  from C. Now, the ordering of vertices in P, gives the optimal ordering of the test vectors such that the maximum Hamming distance between any two consecutive test vectors is minimized. Next we see the second reduction.

#### 3.2.2 Mapping of BTSP to PITMP

In this section, we prove that the BTSP can be reduced to PITMP.

**Input** : An edge-weighted undirected graph G = (V, E)

**Output :** A Hamiltonian path in G, such that the Bottleneck edge-weight is minimized.

#### • The Construction Step :

- 1. Let  $T = t_1, t_2, t_3, ..., t_n$  be a set of test vectors, where  $t_i$  corresponds to  $v_i \in V$  and |V| = n.

- 2. Let  $PIT(t_i, t_j) = e_{ij}$  where  $e_{ij} = w(V_i, V_j)\epsilon E$ .

#### • The Solution Step :

The above construction creates an instance of PITMP. Solve this instance and output ordering of test vectors  $(t'_1, t'_2, t'_3, ...t'_n)$

#### • The Reporting Step :

Output the order of vertices in V, corresponding to the test vector sequence  $(t_1^{'},t_2^{'},t_3^{'},...t_n^{'})$  .

The Solution step shows that the BTSP is solved as an instance of PITMP. The Construction and Reporting steps takes  $O(n^2)$  time. Hence, the BTSP is *polynomially reduced* to an instance of PITMP. Given that the BTSP problem is NP-hard, it is easy to see that PITMP problem is also NP-hard.

Since BTSP is NP-hard, it is important to suggest good heuristics to solve the problem at hand, so that we arrive at fast solutions with reasonable savings in peak input switching activity during testing. The next section explains the BTSP heuristic that we use, to minimize peak input switching activity during testing.

#### **3.3** Algorithm for BTSP

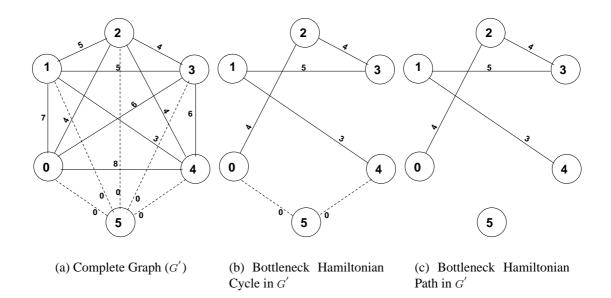

We have used the heuristic proposed by (Larusic *et al.*, 2012) for solving BTSP. This algorithm uses the *Nearest Neighbour Heuristic*(*NNH*) proposed in (Lawler, 1985), for computing upper-bound and *Bottleneck Biconnected Spanning Subgraph*(*BBSS*) algorithm proposed in (Punnen and Nair, 1994) for computing lower-bound. These algorithms are explained in Algorithm 1 and Algorithm 2 respectively. Algorithm 1 finds a Hamiltonian Cycle in a complete graph *G* and returns max cost edge in this cycle. This is an upper-bound for *BTSP* solution. Algorithm 2 finds an biconnected spanning subgraph of *G* by ordering the edges in non decreasing order of edge weights, and does a binary search to find the set of edges in the required biconnected subgraph. To motivate, the bottleneck biconnected spanning subgraph and the nearest neighbourhood of the complete graph in Figure 3.1, are shown in Figures 3.4(a) and 3.4(b) respectively. The BTSP algorithm is shown in Algorithm 3.

\*/

#### Algorithm 1: NNH Algorithm Input: Graph G **Output**: An upper-bound *UB* for *BTSP* Solution 1 / \* Let C be an Hamiltonian cycle in G. Output of this algorithm is maximum cost edge in C. 2 Let current\_vertex be any vertex in graph G and mark current\_vertex as visited : **3** Let *start\_vertex* be *current\_vertex*; 4 Let max\_cost be zero.; **5** while there is any unvisited vertex in graph G do Let V be any unvisited vertex in G such that edge cost between 6 current\_vertex and V is minimum; Let *current\_cost* be edge cost between *current\_vertex*, V; 7

- **s** Let  $max\_cost$  be the  $max(max\_cost, current\_cost)$ ;

- 9 Let  $current\_vertex$  be V;

10 end

- 11 Let *current\_cost* be edge cost between *current\_vertex*, *start\_vertex*;

- 12 Let  $max\_cost$  be the  $max(max\_cost, current\_cost)$ ;

- 13 return max\_cost.

Before going into the details of this algorithm, we will next explain an operation called *Controlled shake operation*, which is extensively used in this algorithm. Let G' be a graph and  $\delta$  be a positive number. *Controlled shake operation* on graph G'with value  $\delta$  creates a graph  $G^s$  as follows

- Vertex set of  $G^s$  is the same as vertex set of G'

- Edge set of  $G^s$  is the same as edge set of G'

- cost of an edge e in  $G^s$  is zero if the cost of the corresponding edge in G' is less than or equal to  $\delta$

- cost of an edge e in  $G^s$  is any positive random number if the cost of the corresponding edge in G' is greater than  $\delta$

Having understood the *Controlled shake operation*, we will now try to briefly understand the different steps in Algorithm 3. A detailed description of the same can be found

#### Algorithm 2: BBSSP Algorithm

**Input**: Graph *G* **Output**: A lower-bound *LB* for *BTSP* Solution

- 1 /\* Let G' be a biconnected spanning subgraph of G such that maximum cost edge in G' is minimum. Output of this algorithm is maximum cost edge in G'. \*/

- 2 Let  $Z_1 < Z_2 < \cdots < Z_k$  be the distinct edge costs of G sorted in increasing order;

- 3 Let l = 1, u = k;

4 while l < u do

$$\begin{split} \delta &= \lfloor \frac{(u-l)}{2} \rfloor + l; \\ G' &= (V, E') \text{ where } E' = \{(i, j) \in E : C_{ij} \leq Z_{\delta} \} \end{split}$$

5 6 if G' is biconnected then 7  $u = \delta;$ 8 end 9 else 10  $l = \delta + 1;$ 11 end 12 13 end 14 return  $Z_l$ .

in (Larusic *et al.*, 2012). The following points summarize the different steps involved in Algorithm 3.

- -----

- Let G<sup>s</sup> be a graph obtained from a graph G' by controlled shake operation with value δ. Note that if G<sup>s</sup> contains Hamiltonian tour with cost zero then G' contains a BTSP tour with cost at most δ.

Suppose BTSP tour cost in a graph G' is  $\leq \delta$ . Then if we apply *controlled shake operation* on G' several times with the same  $\delta$  then one of the graphs generated by these operations will have Hamiltonian tour with cost zero with high probability.

In the algorithm 3, while loop from line 10 to 18 uses these two ideas while trying to find BTSP tour with cost at  $\delta$ . With high probability it will find such a tour if there exists one.

- The *while loop* from line 5 to 26 tries to find an index *i*, where  $1 \le i \le k$ , such that given graph G' contains a BTSP tour with cost at most  $Z_i$  using binary search.

- In line 21 of the algorithm, whenever we are setting upper bound u equal to mid then we are certain that BTSP tour cost in G' is at most  $Z_u$ .

- In line 24 in the algorithm, if we are setting lower bound l to mid + 1 does not mean that BTSP tour cost in G' is at least  $Z_l$ . It can be less than  $Z_l$  with some small probability. This is because we are using a heuristic to test whether the given graph contains a Hamiltonian cycle or not.

(a) Bottleneck biconnected spanning subgraph in G'

(b) Nearest Neighbourhood in G'

Figure 3.4: BBSS and NN in G'

• Whenever this algorithm terminates, lower bound l is equal to upper bound u and given graph contains a BTSP tour with cost at most  $Z_u$ .

Now, the lower bound given by BBSS Algorithm 2 is not a tight lower bound. Keeping this in mind, in order to optimize further, we propose Algorithm 4, which tries to tighten this lower bound value. It compares bottleneck value given by BTSPAlgorithm 3 and maximum cost edge value given by BBSS Algorithm 2, and tries to tighten the lower bound value. We refer to the lower bound thus obtained by Algorithm 4, as *Enhanced lower bound*. In the experimental results, we use this *Enhanced lower bound* to quantify the performance of BTSP Algorithm.

Algorithm 5 explains the entire process of computing bottleneck value.

#### **3.4 Experimental Results**

#### 3.4.1 Experimental Setup

We have considered ITC'99 benchmark circuits listed in table 3.1 for all of our experiments. Each of the ITC'99 benchmark circuit is synthesized using Synopsys<sup>®</sup>Design Compiler with a 45nm standard-cell library. Test vectors were generated for each of the synthesized netlists using *Mentor's FastScan* ATPG tool. The synthesized netlists are taken through Place And Route (PAR) phase using *Cadence Encounter* tool, which is subsequently taken through *Cadence RCXtract* to extract gate and interconnect capacitance values. Next, we explain the results obtained by applying the proposed heuristic on these netlists.

#### 3.4.2 Results

Tables 3.2, 3.3 and 3.4 show the savings in peak input toggles, peak circuit toggles and peak circuit power obtained upon applying the proposed heuristic on benchmark circuits for the cost-functions *primary input toggles, total circuit toggles* and *total circuit power* respectively. In all the three tables, *LB* corresponds to the lower bound obtained using the *Enhanced Lower Bound* Algorithm 4. Similarly *Tool* and *BTSPP* correspond to the peak toggles/power values in the combinational circuit *C* obtained, by applying the test vectors in the order suggested by the  $FastScan^{TM}$  tool and the BTSPP algorithm respectively.

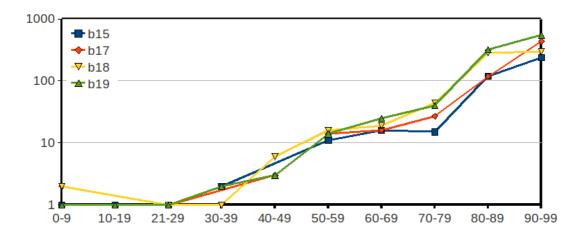

Table 3.2 shows that when *primary input toggles* is used as the cost-function, the peak input-toggles in C, obtained using the BTSPP algorithm is equal to the LB computed, for all benchmark circuits, while the peak input-toggles in C got by applying the test vectors in the order suggested by  $FastScan^{TM}$  is 31.56% higher than LB, on the average. Similarly Table 3.3 shows that when *total circuit toggles* is used as the costfunction, the peak total-toggles in C, obtained by applying the test vectors in the order suggested by the BTSPP algorithm is equal to the lower bound LB value for all benchmarks considered, except b19. In the case of b19, step. 9 in *Enhanced Lower Bound* algorithm ran for many days and did not converge. This step was thus aborted, and the value of  $EW_2$  was assigned to the LB, since  $EW_2$  is also a lower bound to the BT-SPP algorithm. It is interesting to note that although  $EW_2$  (37, 387) was not proved to be a tight lower bound, the peak total toggles in C got by applying vectors in ordering suggested by BTSPP algorithm, in terms of the solution quality. On the other hand, the peak-toggles in C got by applying the test vectors in the order suggested by applying the test vectors in the order suggested by applying the test vectors in the order suggested by BTSPP algorithm, in terms of the solution quality.

$FastScan^{TM}$  is 59.67% higher than LB, on the average. Similarly, Table 3.4 shows that when Circuit Total Power is used as the cost-function, the peak-power dissipated in C by applying the test vectors in the order suggested by the BTSPP algorithm is equal to lower bound LB value for all considered benchmarks, similar to the case of *primary input toggles* (Table. 3.2), while the peak-power dissipated in C got by applying the test vectors in the order suggested by  $FastScan^{TM}$  is 62.99% higher than LB, on the average. Since, total energy consumed by the circuit during capture cycles is dependent on average capture-power, it is interesting to analyze the impact of the ordering suggested by the BTSPP algorithm on *average capture-power*. Table 3.5 shows the results for the same for all the three cost-functions discussed previously. It can be observed that for all benchmarks, for all three cost-values, the average toggles/power values in C got by applying the test vectors in the ordering suggested by BTSPP, is lesser than that got by applying the test vectors in the ordering as suggested by tool. On the average, taken over all benchmark circuits, the reduction in average toggles/power for the three costvalues was 27.2%, 27.8% and 28.3% respectively when compared with those yielded by the commercial tool.

#### Algorithm 3: BTSP Algorithm

### Input: Graph G' Output: Bottleneck Edge

- 1 Compute lower-bound *lb* and upper bound *ub* using Bottleneck Biconnected Spanning Subgraph Problem (BBSSP) algorithm and Nearest Neighbour Heuristic (NNH) respectively in given graph G';

- 2 Let  $Z_1 < Z_2 < \cdots < Z_k$  be an ascending arrangement of the distinct edge costs in graph G' such that  $Z_1 \ge lb$  and  $Z_k \le ub$ ;

- 3 /\* find an index i, where  $1 \le i \le k$ , such that given graph G' contains a BTSP tour with cost at most  $Z_i$ using binary search \*/ 4 Let  $l \leftarrow 1, u \leftarrow k$ ;

```

5 while l < u do

```

```

6 mid \leftarrow \lfloor (l+u)/2 \rfloor;

```

```

7 count \leftarrow some positive integer say N;

```

**8**  $flag \leftarrow 1$ ;

```

9 \delta \leftarrow Z_{mid};

```

11

12

15

```

while count > 0 and flag = 1 do

```

```

Apply controlled shake on graph G' with value \delta to get graph G^s;

```

```

Find a lowest cost TSP tour in G^s using Lin-Kernighan TSP heuristic;

```

```

13 Let T be this tour ;

```

```

14 if the length of T is zero then

```

$$flag \leftarrow 0$$

16 end

```

17 | count \leftarrow count-1;

18 | end

```

```

18 end

```

```

19 if flag = 0 then

20 u \leftarrow mid;

```

```

21 end na

```

```

21 ella

22 else

```

```

23 | l \leftarrow mid+1;

```

```

24 end

```

```

25 end

```

**Result**: BTSP cost is equal to  $Z_u$ .

Algorithm 4: Enhanced Lower Bound Algorithm

```

Input: TVG of a combinational circuit C constructed for a given set of test

vectors T

Output: An Enhanced Lower Bound LB

1 Solve the BTSPP on TVG as described earlier. Let the maximum weight of

any edge on the computed Bottleneck Traveling Salesman Path be EW_1;

2 Compute BBSS(TVG); Let the maximum weight of any edge on

BBSS(TVG) be EW_2;

3 / * When the cost of the bottleneck edge(EW_1) is same

as max cost edge in Biconnected spanning subgraph

(EW_2) then the solution given by BTSP is

optimal solution, and max cost edge in Biconnected

spanning subgraph is greatest lower - bound

*/

4 if EW_1 == EW_2 then

5 LB \leftarrow EW_1;

6 end

7 if EW_1 > EW_2 then

Remove all edges in TVG with edge-weight greater than or equal to EW_1.

8

Let the new graph be G':

Test if G' has a Hamiltonian cycle using the methodology suggested in

9

(Vandegriend, 1998);

if G' does not have a Hamiltonian cycle then

10

/* Since G' does not have a Hamiltonian cycle the

11

solution given by BTSP is optimal solution,

hence the greatest lower - bound value is EW_1 * /

LB \leftarrow EW_1;

12

end

13

else

14

/* Since G' has a Hamiltonian cycle the solution

15

given by BTSP might not be optimal solution,

hence the lower - bound value is at least EW_2 * /

LB \leftarrow EW_2;

16

end

17

18 end

19 return LB:

```

26

Algorithm 5: BTSPP Algorithm **Input**:  $\pi = \{T_1, T_2, ..., T_n\}$  set of completely specified test vectors **Output:**  $\pi' = \{T_1, T_2, ..., T_n\}$  sequence of completely specified test vectors 1 Let  $T_i...T_k$  be the set of test vectors of Circuit C 2 Let  $c_{i,j}$  be the cost of applying test vector j after i,  $c_{j,i}$  be the cost of applying test vector *i* after *j*.Note that  $c_{i,j}=c_{j,i}, 1 \le i \le k; 1 \le j \le k; i \ne j$ . 3 / \* Construct a Graph G as follows \*/ 4 Let  $\{v_1...v_k\}$  be the vertex set of G. Note that vertex  $v_i$  corresponds to test vector  $T_i$ , for  $1 \le i \le k$ . s Place an edge between  $v_i, v_j$  whose cost is  $c_{ij}, \forall i, j. 1 \le i \le j \le k$ . 6 /\* Construct a Graph  $G^{\prime}$  as follows \*/ 7 Add an vertex  $v_{k+1}$  to G. s Place an edge between  $v_{k+1}, v_i$  in G with a cost zero,  $\forall i, 1 \leq i \leq k$ . 9 Compute lower bound LB and upper bound UB using Bottleneck Biconnected Spanning Subgraph ProblemBBSSP Alogrithm and Nearest Neighbor Heuristic(NNH) respectively in given graph G'. 10 Let  $Z_1 < Z_2 < ... < Z_k$  be an ascending arrangement of the distinct edge costs in graph G' such that  $Z_1 > LB$  and  $Z_k < UB$ . 11 Let l = 1, u = k12 while l < u do Let mid = (l + u)/2) 13 /\* Construct a graph  $G^s$  as follows \*/ 14 Vertex set of  $G^s$  is the same as vertex set of G'15 Edge set of  $G^s$  is the same as edge set of G'16 Cost of an edge e in  $G^s$  is zero if the cost of the corresponding edge in G' is 17 less than or equal to  $Z_{mid}$ . Cost of an edge e in  $G^s$  is any positive random number if the cost of the 18 corresponding edge in G' is greater than  $Z_{mid}$ . Find a lowest cost TSP tour in  $G^s$  using Lin - Kernighan TSP heuristic. 19

```

20 if tour lenght = 0 then

```

```

21 Let u = mid;

```

```

22 else

```

```

23 | Let l = mid + 1;

```

```

24 end

```

```

25 end

```

- 26 Let P be a path in G' obtained by removing vertex  $v_{k+1}$  from TSP tour. Note that P is a Hamiltonian path in G such that cost of any edge is atmost  $Z_u$ .

- 27 Ordering of the vertices in path P gives the required test vector ordering such that  $peak \ cost$  is at most  $Z_u$ .

| Circuit | # PIs | #Gates  | # Test Vectors |

|---------|-------|---------|----------------|

| b01     | 5     | 57      | 17             |

| b02     | 4     | 31      | 11             |

| b03     | 29    | 103     | 16             |

| b04     | 77    | 615     | 98             |

| b05     | 35    | 608     | 81             |

| b06     | 5     | 60      | 19             |

| b07     | 50    | 431     | 61             |

| b08     | 30    | 196     | 49             |

| b09     | 29    | 162     | 33             |

| b10     | 28    | 217     | 54             |

| b11     | 38    | 574     | 104            |

| b12     | 126   | 1.6K    | 118            |

| b13     | 53    | 396     | 44             |

| b14     | 275   | 5.4K    | 658            |

| b15     | 485   | 8.7K    | 594            |

| b17     | 1452  | 28K     | 786            |

| b18     | 3357  | 75.8K   | 913            |

| b19     | 6666  | 146.52K | 1,147          |

| b20     | 522   | 9.4K    | 652            |

| b21     | 522   | 9.4K    | 671            |

| b22     | 767   | 13.4K   | 589            |

Table 3.1: ITC'99 Benchmarks

| Circuit | LB    | Tool  | BTSPP | % gap v | with LB | Run Time |

|---------|-------|-------|-------|---------|---------|----------|

|         |       |       |       | Tool    | BTSPP   |          |

| b01     | 2     | 5     | 2     | 150.00  | 0.00    | 0.04s    |

| b02     | 2     | 4     | 2     | 100.00  | 0.00    | 0.05s    |

| b03     | 7     | 11    | 7     | 57.14   | 0.00    | 0.34s    |

| b04     | 31    | 49    | 31    | 58.06   | 0.00    | 2.01s    |

| b05     | 12    | 24    | 12    | 100.00  | 0.00    | 0.33s    |

| b06     | 2     | 4     | 2     | 100.00  | 0.00    | 0.06s    |

| b07     | 19    | 34    | 19    | 78.95   | 0.00    | 1.33s    |

| b08     | 11    | 21    | 11    | 90.91   | 0.00    | 0.22s    |

| b09     | 10    | 21    | 10    | 110.00  | 0.00    | 0.05s    |

| b10     | 11    | 19    | 11    | 72.73   | 0.00    | 1.52s    |

| b11     | 14    | 27    | 14    | 92.86   | 0.00    | 0.88s    |

| b12     | 53    | 79    | 53    | 49.06   | 0.00    | 1.00s    |

| b13     | 21    | 34    | 21    | 61.90   | 0.00    | 0.11s    |

| b14     | 114   | 158   | 114   | 38.60   | 0.00    | 4.47m    |

| b15     | 216   | 280   | 216   | 29.63   | 0.00    | 2.97m    |

| b17     | 679   | 785   | 679   | 15.61   | 0.00    | 22.93s   |

| b18     | 1,601 | 1,760 | 1,601 | 9.93    | 0.00    | 3.18m    |

| b19     | 3,218 | 3,447 | 3,218 | 7.12    | 0.00    | 15.20m   |

| b20     | 231   | 294   | 231   | 27.27   | 0.00    | 16.70s   |

| b21     | 228   | 294   | 228   | 28.95   | 0.00    | 4.06m    |

| b22     | 349   | 512   | 349   | 46.70   | 0.00    | 13.76s   |

| Average | -     | -     | -     | 31.56   | 0.00    | 1.47m    |

Table 3.2: Edge cost : Primary input toggles per vector pair

| Circuit | LB     | Tool   | BTSPP  | % gap  | with LB | Run Time |

|---------|--------|--------|--------|--------|---------|----------|

|         |        |        |        | Tool   | BTSPP   |          |

| b01     | 21     | 37     | 21     | 76.19  | 0.00    | 0.02s    |

| b02     | 13     | 18     | 13     | 38.46  | 0.00    | 0.07s    |

| b03     | 29     | 52     | 29     | 79.31  | 0.00    | 0.07s    |

| b04     | 226    | 375    | 226    | 65.93  | 0.00    | 0.68s    |

| b05     | 189    | 323    | 189    | 70.90  | 0.00    | 2.81s    |

| b06     | 18     | 39     | 18     | 116.67 | 0.00    | 0.02s    |

| b07     | 143    | 252    | 143    | 76.22  | 0.00    | 0.15s    |

| b08     | 64     | 119    | 64     | 85.94  | 0.00    | 1.28s    |

| b09     | 51     | 107    | 51     | 109.80 | 0.00    | 0.70s    |

| b10     | 66     | 132    | 66     | 100.00 | 0.00    | 1.36s    |

| b11     | 154    | 264    | 154    | 71.43  | 0.00    | 5.32s    |

| b12     | 443    | 682    | 443    | 53.95  | 0.00    | 3.49s    |

| b13     | 149    | 212    | 149    | 42.28  | 0.00    | 0.17s    |

| b14     | 1,565  | 2,449  | 1,565  | 56.49  | 0.00    | 16.77s   |

| b15     | 2,078  | 3,148  | 2,078  | 51.49  | 0.00    | 8.90m    |

| b17     | 7,125  | 9,217  | 7,125  | 29.36  | 0.00    | 15.68m   |

| b18     | 20,103 | 24,694 | 20,103 | 22.84  | 0.00    | 27.81s   |