# Low Power Personalized ECG Based System Design Methodology for Remote Cardiac Health Monitoring

Naresh Vemishetty, Pravanjan Patra, Pankaj Kumar Jha, Krishna Bharadwaj Chivukula, Charan Kumar Vala, Agathya Jagirdar, Venkateshwarlu Y Gudur, Amit Acharyya, *Member, IEEE* and Ashudeb Dutta, *Member, IEEE*

Abstract—This paper describes a mixed-signal ECG system for personalized and remote cardiac health monitoring. The novelty of this work is four-fold. Firstly, a low power analog front end with an efficient automatic gain control mechanism, maintaining the input of the ADC to a level rendering optimum SNR and the enhanced recyclic folded cascode opamp used as an integrator for  $\Sigma\Delta$  ADC. Secondly, a novel on-the-fly PQRST Boundary Detection (BD) methodology is formulated for finding the boundaries in continuous ECG signal. Thirdly, a novel low-complexity ECG feature extraction architecture is designed by reusing the same module present in the proposed BD methodology. Fourthly, the system is having the capability to reconfigure the proposed Low power ADC for low (8 bits) and high (12 bits) resolution with the use of the feedback signal obtained from the digital block when it is in processing. The proposed system has been tested and validated on patient's data from PTBDB, CSEDB and in-house IIT Hyderabad DB (IITHDB) and we have achieved an accuracy of 99% upon testing on various normal and abnormal ECG signals. The whole system is implemented in 180 nm technology resulting in 9.47 $\mu$ W (@ 1 MHz) power consumption and occupying 1.74mm<sup>2</sup> silicon area.

Index Terms—ECG, Boundary Detection, Feature Extraction, Discrete Wavelet Transform, Cardiovascular Disease.

#### I. INTRODUCTION

MONG the several non-communicable diseases world is scourged with Cardiovascular Diseases (CVD) resulting in millions of deaths every year throughout the globe [1]. There is an exponential increment in human mortality rate, caused due to the delayed diagnosis, lack of proper distribution of health care facilities and prognosis centers in the vicinity. There is a need of a robust automated device for the early detection of the vital abnormal ECG signals in chronic CVD patients. To address the aforementioned problems, there is a tremendous necessity of developing a personalized CVD monitoring device powered by battery backup and with a very low form factor to achieve unobtrusiveness that works under the emerging cyber-physical system setup. This medical science and technological needs impose many challenges on such device development viz., low power consuming system design tradeoff between the on-board processing and RF communication, low complexity analog front end circuit design

N.V, P.P, P.K.J, K.B.C, C.V, A.J, V.Y.G, A.A, A.D are with the Department of Electrical Engineering, Indian Institute of Technology, Hyderabad, Telangana, 502285 INDIA

emails: (ee14resch01003, ee13P0006, ee10P007, ee14mtech01008, ee15resch02009, amit\_acharyya, asudeb\_dutta)@iith.ac.in, bharadwa-jchivukula@yahoo.com, agathya.jagirdar@gmail.com

and energy harvesting or self-power mechanism to prolong battery life. In this paper, our emphasis is on proposing a low complexity system with on-board processing methodology, preceded by a low power analog module targeting remote and personalized CVD monitoring. Although the existing analog front-ends [2] fulfill the processing requirement, but it suffers from a major drawback of high power consumption which leads to fast draining of battery. To overcome this, and hence ensure prolonged operation of the monitoring device, each constituent block of the AFE is designed using the gm/ID optimization technique. This technique helps in the sizing the individual MOSFETs, such that the power consumption and noise levels are within the desired specifications. Further, to ensure a reliable operation of the AFE, the performance parameters individual blocks are verified across process, voltage, and temperature variations. On the other hand, main research thrust has been given so far on the low power feature extraction mechanisms [3], [4] where the objective was to obtain several ECG characteristic features (P, Q, R, S, T) by proposing a methodology which could be implemented on either microcontroller or FPGA or an ASIC platform resulting in low power consumption. However, all of these mechanisms [5], [6] have considered the ECG boundary containing all the required features will be supplied from some other process or module and hence has not been taken into consideration while doing the power budgeting and the hardware complexity analysis. Although such robust boundary detection approach would significantly impact the accuracy of the subsequent feature extraction modules, but definitely at the cost of higher circuit complexity resulting in higher power consumption than what reported in the literatures [7], [8]. Hence, in this paper, we propose the following:

- a low power AFE, with an efficient automatic gain control mechanism which maintains the input of the ADC to a level rendering optimum SNR. The enhanced recyclic folded cascode opamp is used for the implementation of the required integrators for  $\Sigma\Delta$  ADC (section II-A).

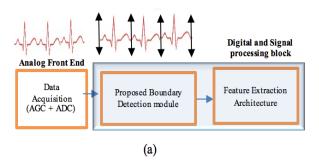

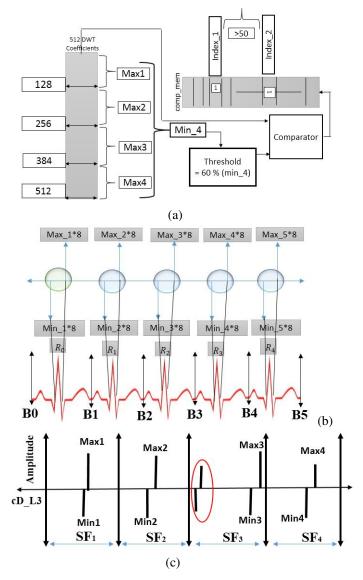

- the proposed methodology for finding the boundaries of ECG signal (starting and ending index of the single heart beat) as shown in Fig.1 (a) (section II-B).

- a novel low complexity architecture of ECG feature extraction by reusing the same module used in the proposed Boundary Detection (BD) methodology (section II-B). Unlike the state-of-the-art (SoA) architectures [3], the

Fig. 1. (a) Block representation of the proposed analog and digital and signal processing modules including proposed BD and FE (b) Architectural block diagram of the proposed system

proposed architecture performs both BD and Feature Extraction (FE) together using only one Discrete Wavelet Transform (DWT) core as shown in Fig.1 (b).

The rest of the paper is organized as follows. Section II introduces the proposed methodologies and architecture design, section III presents the experimental results and section IV concludes the paper.

## II. PROPOSED METHODOLOGY

Figure.1 (b) represents the block diagram of the proposed personalized remote CVD monitoring system. As shown in the Fig.1 (b), a nalog block comprising of Automatic Gain Control (AGC), reconfigurable ADC and getting continuous feedback switching resolution signal from the digital block. As shown in Fig.1 (b) the AGC is responsible for setting the gain of the Programmable Gain Amplifier (PGA) such that the input ECG signal is amplified to a level for which the ADC achieves its maximum SNR. The ADC is activated only when the AGC completes its operation. The ADC dumps the digital samples into a memory of fixed size. The ADC

#### TABLE I LIST OF ABBREVIATIONS

AFE: Analog Front End AGC: Automatic Gain Control ARM: Advanced RISC Machines

ASIC: Application Specific Integrated Circuits

BD: Boundary Detection. CL: Load Capacitance

CIFB: Cascaded Integrator Feedback

CLU: Control Logic Unit

CIC: Cascaded IntegratorComb

cD\_Lk: Level k Detailed Coefficients

CMRR: Common Mode Rejection Ratio

CSE: Common Standards in Quantitative Electrocardiography

CVD: Cardiovascular Disease

DB: Data Base DR: Dynamic range DT: Discrete Time

DWT: Discrete Wavelet Transform

ECG: Electrocardiogram

ERFC: Enhanced Recyclic Folded Cascode FPGA: Field Programmable Gate Array

FE: Feature Extraction

MMA: Maximum Modulus Analysis

OTA: Operational Transconductance Amplifier

PGA: Programmable Gain Amplifer

PTB: Physikalisch -Technische Bundesanstalt

PSD: Power Spectral Density

RE: Rule Engine

RFC: Recyclic Folded cascode SAR: Successive Approximation SFDR: Spurious-Free Dynamic Range

SF: Sub Frame

resolution is adjusted on the fly with a feedback signal from the Control Logic Unit (CLU) based on the classification of the ECG signal. Digital block comprises of the proposed BD, FE and the low complexity DWT core as the main processing unit (shown in bold in Fig.1 (b)) alongside it has a CLU, memory, and an intelligent rule engine [9] which would estimate the trade-off between the on-board process and RF communication (Bluetooth low energy/ Zigbee/WiFi) to either smartphone or tablet or cloud under the cyber-physical system framework as shown in Fig.1 (b). Rule Engine (RE), as seen in Fig.1 (b), decides the abnormality of the signal based on the extracted features [25], [26] and takes an intelligent decision dynamically on the trade-off between on-board processing or RF communication [9].

A. Ultra low power analog front end for acquisition and digitization

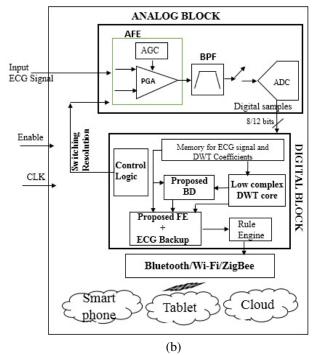

The prime features of the Analog Front End (AFE) as shown in Fig.2 (a) are:

- (a) An ultra-low power two stage capacitive-coupled signal conditioning circuit providing programmable amplifications and tunable 2nd order highpass and lowpass characteristics.

- (b) An efficient AGC mechanism maintaining the input of the ADC to a level rendering optimum SNR. In all of the acquisition schemes (even those where gain is controlled via DSP) reported till date, the ADC is kept continuously. Hence, the present scheme is designed to consume less power than the conventional ones because (i) ADC is turned on only after AGC has finished its job, and (ii) it avoids gain control through

Fig. 2. (a) Block diagram of the proposed acquisition system. (b) Analog front-end providing both amplification and LPF and HPF characteristics. (M=10, N=8,  $C_U$ =1.03pF,  $C_g$ =103fF, and  $C_L$ =2-12pF). (c)Block diagram of the peak detector and voltage level detector. (d) Single ended representation of the fully differential opamp shared DT  $\Sigma\Delta$  ADC. The circuit renders 1st order noise shaping when only components in black color are activated, and 2nd order noise shaping when the components in dark red are also activated. Here  $C_{S1}$ =0.67pF,  $C_{S2}$ =2.02pF,  $C_{Sfb}$ =0.79pF,  $C_{i1}$ =4pF, and  $V_{cm}$ = 0.9V.

- a DSP which is very power hungry [12].

- (c) A low power, high resolution  $\Sigma\Delta$  ADC achieving  $2^{nd}$  order noise shaping while using a single integrator.

- (d) Seamless  $\Sigma\Delta$  ADC resolution reconfigurability with minimal hardware and almost zero power overhead. This facilitates the digital circuit, following the  $\Sigma\Delta$  ADC, to reduce its power

consumption by opting to process low-resolution data. The proposed  $\Sigma\Delta$  ADC implementation aids area and power cost-

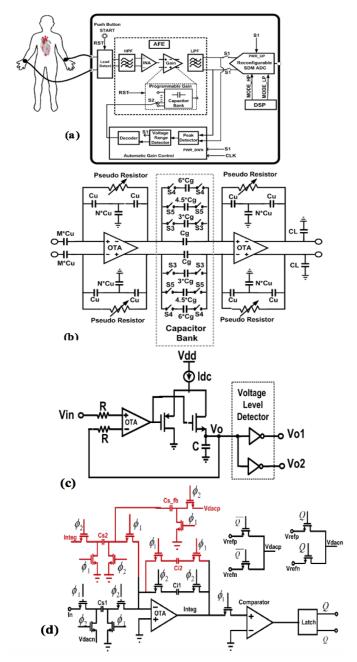

Fig. 3. (a)Frequency response of the AFE. The high pass cut-off frequency is tuned by the gate potential of the pseudo-resistor. Different high pass cut-off frequency for different values of gate potentials is shown. (b) The waveforms of the scaled input ECG signal taken from PTB database (top) and the output signal reconstructed using CIC filter (bottom). (c)PSD of the opamp shared  $\Sigma\Delta$  ADC for an input of -5.2dB.

efficient switching between the two modes vis-a-vis other ADC architectures e.g. SAR ADC, pipeline ADC, etc. [13].

1) Signal Conditioning Stage with Programmable Gain and Tunable Bandwidth: The proposed low power AFE provides the required gain and the bandpass filter characteristics. Fig.2 (b), shows the schematic of the AFE. The heart of each of the stages is a fully differential Recyclic Folded Cascode (RFC) OTA adopted from [14]. Reconfigurability can be introduced in the AFE by incorporating the features of programmable gain and tunable bandwidth, hence extending its utility for the acquisition of various biopotential (ExG) signals. The voltage gain of the closed loop amplifier is varied by changing the feedback factor. While the high pass cutoff frequency is varied by changing the gate voltage of the pseudo-resistor, the lowpass cut-off frequency is varied changing the load capacitance CL [16]. Further, a T-feedback network is used to reduce the effective feedback capacitance so that the same

gain can be achieved with much smaller capacitance [17]. The frequency response of the AFE is shown in Fig. 3(a) indicates the utility of this system for the acquisition of various ExG signals.

- 2) Automatic Gain Control: Since the input voltage of the subsequent  $\Sigma\Delta$  ADC needs to be maintained at an optimum level, the gain of this stage needs to be controlled. The output level of the AFE is controlled by the AGC stage, shown in Fig. 2(c), by selecting the appropriate combination of capacitors from the capacitor bank [18] as shown in Fig.2(a). The AGC comprises of a peak detector, a voltage range detector, a fully digital decoder modeled as a Moore machine and a logic isolation block. The isolation block:

- (i) decouples the gain control mechanism from the analog front end.

- (ii) forwards the output of the AFE to the ADC, once the input falls in the desired amplitude range.

- 3)  $\Sigma \Delta ADC$  design:  $\Sigma \Delta ADC$  digitizes the AFEs output so that it can be taken up by the digital module. A conventional Discrete Time (DT) Cascaded Integrator Feedback (CIFB)  $\Sigma\Delta$ ADC modulator with  $2^{nd}$  order noise shaping is chosen for this work. Owing to the fact that the integrator is the most power hungry block of the  $\Sigma\Delta ADC$ , two-fold strategy was employed to minimize the ADC power consumption. Firstly, the whole ADC was designed for minimum current as possible, keeping the target SNR intact. Second, the  $2^{nd}$  order noise shaping was achieved using only a single integrator, which reduces the power consumption to nearly half that of the ADC employing two integrators as shown in Fig.2(d) [14]. The integrator is implemented using the enhanced recyclic folded cascode (ERFC) [10], [11]. The ERFC OTA has twice the bandwidth of a conventional folded cascode OTA for the same power and area. The plot for spectral density of the ADC output is shown in Fig. 3(c). The figure clearly shows that the ADC renders 2nd order noise shaping and SFDR of 70dB.

- 4) Seamless ADC Resolution Reconfigurability: The output of the  $\Sigma\Delta ADC$  is taken up by the subsequent digital circuit for relevant signal processing like classification and feature extraction. Since the power consumed by this digital circuit is proportional to the resolution of the data it is processing, the digital circuit may opt to reduce its power consumption by reducing the resolution of the data it is processing. A control signal from the digital circuit selects the output resolution of the  $\Sigma\Delta ADC$ . The proposed  $\Sigma\Delta ADC$  is designed to work in two modes controlled by the DSP (i) the low-resolution (8 bits), and (ii) high-resolution (12 bits) mode. In the lowresolution mode, the  $\Sigma\Delta$  modulator provides  $1^{st}$  order noise shaping using one integrator whereas in the high-resolution mode, the  $\Sigma\Delta ADC$  modulator provides  $2^{nd}$  order noise shaping while using only a single integrator. Since integrators are the most power hungry circuits in the  $\Sigma\Delta$ ADCs, here, a higher resolution is extracted keeping the power consumption nearly the same.

#### B. Proposed on the fly Boundary Detection methodology

As shown in the Fig.1 (b) Haar-based DWT core will be shared by the proposed BD and FE modules. The proposed BD

Fig. 4. BD Pseudo code block representation (a)Block till finding the actual maximas in  $cD\_L3$  coefficients. (b)Projection of Max and Min coefficients to ECG memory. (c)Max and Min pairs in  $cD\_L3$  coefficients..

methodology works on the R-Peak and boundary estimation from an ECG signal. To get the optimum R-peak, the analysis has to be performed on third resolution level of DWT, it has filter bank structure with a cascaded high pass (h[n]) and low pass (l[n]) filters [3] and at every stage we get the half the number of coefficients as output w.r.t the number of samples at the filter input. It is to be noted that, to keep the computational complexity low in terms of required mathematical operations, we have selected the Haar wavelet the simple wavelet function.

Haar wavelet removes the noise and isoelectric line wandering of ECG signals, which is shown to be more suitable for health monitoring applications [3].

To begin, 'N' ECG samples  $[ECG\_data]$  has been applied as input to the first level of DWT, due to the downsampling after every stage of the filter gives  $N/2^L$  coefficients as output, here 'L' represents the resolution level of DWT, the number of output coefficients obtained at the third resolution level are

```

Algorithm 1 Pseudo code for Boundary Detection

```

```

Require: Boundaries of each ECG beat to be calculated.

1: ECG\_data = load(.matfile) {N=4096 ECG data}

2: for i = 1 \ to \ N do

cD L3 = Third\ level\ haar\ dwt(ECG\ data)

Fifth\ level\ haar\ dwt(ECG\ data)

\{cD\_L3, cD\_L5\}

results 512 & 128 coefficients

respectively }

5: end for

6: min_4 = min(max(cD_L3(1:128), max(cD_L3(129:

256), max(cD_L3(257:384), max(cD_L3(385:512))

7: Th = 60\%(min\_4)

for i = 1 to length(Third\_level\_haar\_dwt) do

if (cD_L3(i) > Th) then

Comp\_mem[i] = 1

10:

else

11:

Comp\_mem[i] = 0

12:

end if

13:

14: end for

15: for i = 1 to length(Third\_level\_haar\_dwt) do

if Comp mem (i) ==1 & Comp mem (i+1)==1) then

16:

Comp\ mem(i) = 0

17:

18:

i = i + 1

19:

else

Comp\_mem(i) = Comp\_mem(i)

20:

i = i + 1

21:

end if

22:

23: end for

for i = 1 to length(Third\_level\_haar\_dwt) do

24:

25:

if (Comp\_mem == 1) then

Comp\_mem = i

26:

i = i + 1

27:

end if

28:

29: end for

30: for j = 1 to length(cd_3\_logic\_location) do

31:

((Comp mem location(j

1)

Comp\_mem\_location(j)) > 50 then

store\_index(j) = Comp\_mem\_location(j)

32:

33:

34.

else

35:

store\_index(j) = cd\_3\_logic\_location(j + 1)

j = j + 1

36:

end if

37:

38: end for

39: for i = 1 to length(store\_index) do

R_Peak[i]=abs(ECG_data(((min((cD_L3(store_index

(i)-10)):(cD_L3(store_index (i)+10)))*8):((store_index

(i)+10)*8)))

41: end for

42: if ((R_Peak(1)-1)=(R_Peak(1)+R_Peak(2))/2))

first\_Boundary = (R\_Peak(1) - (R\_Peak(1) +

43:

R_Peak(2))/2)

44: else

first\_Boundary = first\_Boundary

45:

46: end if

=0

```

```

\begin{array}{ll} \textbf{if} & length(ECG\_data) & - & R\_Peak(end) \\ & (R\_Peak(end) - R\_Peak(end-1))/2 \textbf{ then} \\ & last\_Boundary = R\_Peak(end) + ((R\_Peak(end) - R\_Peak(end-1))/2) \\ \textbf{else} \\ & last\_Boundary = last\_Boundary \\ \textbf{end if} \\ \textbf{for } i = 1 \ to \ length(R\_Peak) - 1 \ \textbf{do} \\ & Boundary[i] = (R\_Peak(i) + R\_Peak(i+1)/2) \\ \textbf{end for=} 0 \end{array}

```

$N / 2^3$ . Considering N = 4096 ECG samples results in 512 detailed ( $cD_L 23$ ) from high pass, please see the line number 4 of Algorithm 1. The corresponding equations of the filters are (1) and (2), where 'i' = 0, 1, 2, 3,....(N-1) ECG Samples from ADC.

$$h_L[n] = \frac{1}{\sqrt{2}} \left( \left( E_i[2n+1] + E_i[2n+2] \right) \right)$$

(1)

$$h_L[n] = \frac{1}{\sqrt{2}} \left( (E_i[2n+1] - E_i[2n+2]) \right)$$

(2)

where n= 1 to  $\frac{N}{2} - 1$

Here 'L' represents the resolution level of DWT. In the above equation, the factor  $1/\sqrt{2}$  can be eliminated because it is just a constant multiplication factor for all the samples which does not change the morphology of the input ECG signal. Possibility to obtain R-peak when the ECG is sampled at 1 KHZ is at least once in 1024 samples, therefore, to get the R-peak, (cD L3) coefficients are divided into m = N / 1024(sampling rate) subframes, as N = 4096 the  $cD_L3$  coefficients should be divided into 4 sub-frames as shown in Fig.4(c) where each sub-frame holds  $N/(2^LXm)$  coefficients i.e. each sub-frame consists of 128 coefficients for N = 4096. N is chosen as 4096 because there will be at least three frames (heart beats) in 4096 samples, to get boundaries of a single heart beat there should be a minimum requirement of at least three frames, so this made us to take 4096 ECG samples in the design. Keeping in the mind of architectural implementation, we have not increased the depth more than 4096 samples, as the increment in memory depth will lead to the increment in area and power consumption of the design. In Alogorithm 1,  $cD_{L}3(1:128)$  to  $cD_{L}3(384:512)$  are the sub-frames please see the line number 7. Getting the maximum index from all the sub-frames are shown in Algorithm 1, please see the line number 7. While finding the maximum and minimum pairs there is possibility of missing some other pair in the SF which are highlighted in red color as shown in Fig.4(c). We can capture those pairs based on two factors, 1) the amplitude value of the maximum missing coefficient should be least 60% of the min 4 (Please see the Algorithm 1, line number 8) which is called threshold value. 2) The index difference between the missing pair and the pre and post pairs should be greater than the value 50. The threshold is calculated as follows: Th = K% (min\_4). Here the value K= 60%, as the value is taken based on the statistical analysis performed on the three databases (PTBDB, CSEDB and IITH DB), there is a chance of detecting the noise if the threshold value is less than 60%. The logic to adopt the hard value 50 is obtained based on the number of ECG samples between consecutive R-peaks at the third level of DWT.

The minimum number of samples in the consecutive R-peak under 1 kHz sampling frequency are 400. Since the analysis is performed on the third resolution, the R-peak equivalent points in DWT domain will have to scale down proportionally, therefore level 3 DWT the scaled factor will be  $2^3$  therefore,  $400/2^3$  results in the value 50. The value 400 will be changed if the digital samples are coming at different sampling rate other than from 1 KHz. Therefore, the occurrence of successive maximums will be greater than 50 samples difference in level 3 detailed coefficients of DWT as shown in Fig.4 (a). The Comparator has been taken to compare all 512 cD\_L3 coefficients with the threshold value and gives an outcome as '1'if the coefficient value is greater than the threshold else, the outcome is '0', it is clearly shown in Fig.4 (a) and explained in the line number 9 to 14 of Algorithm 1. The output of the comparator '1's and '0's will be stored in the memory (comp\_mem) whose depth is 512 with word length of 1 bit. To find the missing maximum coefficients in cD\_L3 coefficients, count the number of '1's in the 'comp\_mem'such that the index difference between the two successive '1's should be greater than 50 as shown in Fig 4 (a) and Algorithm 1, please see the line number 32.

In the Fig.4 (a) the difference between the index\_1 and index\_2 is greater than 50, this signifies index\_1 is one of the maximum coefficients in the cD\_L3 and its value has to be stored in a memory (store index) Algorithm 1, please see the line number 32. Similarly, other maximum coefficients have been calculated and stored in 'store\_index'memory of variable depth 4 to 7, 'mem\_max'depth depends on the number of pairs occurring in cD\_L3 coefficients. For every maximum index there is a minimum index nearby  $(\pm 10)$  maximum in cD L3 coefficients, hence we get the minima's as explained in Algorithm 1, please see the line number 40. The value 10 has been taken on statistical analysis, by observing various ECG signals. The R-peak has been calculated by projecting maxima and minima values to the ECG memory as explained in Algorithm 1, please see the line number 40 and it is clearly shown in the Fig.4(b). The boundaries are calculated by taking the average over R-peaks as explained in Algorithm 1, please see the line number 54. In the real time, ECG wave may start at any point within P, Q, R, S, T and the ECG signal may or may not have the initial (B0) and final (B5) boundaries as shown in Fig.4(b). Line number 42 to 53 of Algorithm 1 explains the condition about the occurrence of first (B0) and last boundary (B5) of continuous ECG signal.

The existing feature extraction algorithm [3] has applied Maximum Modulus Analysis (MMA) on cD\_L3 to get the temporal boundaries let say, t1 and t2 as shown in fig.4(c). These algorithms used to calculate R-peak based on conditions whether t1 < t2 or t1 > t2. In the proposed algorithm, there is no necessity to check these conditions, instead, left shift the t1 and t2 by three times, say x1=(t1<<3) and x2=(t2<<3) to get the R- peak and find the absolute value in the ECG memory within the range x1 and x2, resulting in the hardware

optimization upon ignoring the conditions. The accuracy of the algorithm has been improved at the stage of finding the  $P \ / \ T$  waves, where the existing algorithms [3] analyzed the extraction of  $P \ / \ T$  at fifth level by considering the  $QRS_{on}$  and  $QRS_{off}$  obtained at the third. To find the exact values of  $P \ / \ T$ , the values of  $QRS_{on}$  and  $QRS_{off}$  values should be divided by  $2^2$  since analyzing is done at fifth level, which improves the accuracy and also the low complexity is achieved by discarding the LSB bits instead of division hardware and right shifting.

# Algorithm 2 Pseudo code for extracting Features

**Require:** Features of one ECG beat are calculated. {We got R-Peak  $R_0$ , boundaries  $B_0$  and  $B_1$  from afore mentioned Boundary Detection Algorithm}

```

1: if R_0 >= 0 then

Q\_Peak = min(ECG\_samples(((QRS\_on) * 8) :

3: else

Q\_Peak = max(ECG\_samples(((QRS\_on) * 8) :

R(0)

4: end if

5: if R_0 >= 0 then

S Peak

min(ECG\_samples(((R\_0

(QRS\_off) * 8))

7: else

S_Peak

max(ECG\_samples(((R\_0

(QRS\_off) * 8))

8: end if

9: max \ p = max(cD \ L5(1 : QRS \ on/4))

10: min_p = min(cD_L5(1 : QRS_on/4))

11: P Peak =

abs(ECG\_Samples((min\_p * 32)

(max_p * 32))

12: max_T = max(cD_L5(QRS_off/4:1))

13: min \ T = min(cD \ L5(QRS \ of f/4:1))

14: T\_Peak = abs(ECG\_Samples((min\_T * 32)))

(max \ T*32)))

=0

```

#### C. Low complexity Feature Extraction architecture

The obtained start and end boundaries and R\_peaks as shown in Fig.4 (b) from the boundary detection methodology will be given as input to FE module. The remaining features to be extracted are QRS complex and P/T intervals and their indices from the main memory (ECG memory) of all the frames. The following explanation of Algorithm 2 is for one frame and the same applies to all other frames extracted from BD algorithm. To identify the QRS boundaries  $QRS_{on}$ and  $QRS_{off}$  we have adopted the concept from [3]. In this methodology, the accuracy is achieved along with architecture optimization in extracting the 'Q' and 'S' indices and P/Twave intervals along with their exact indices. Generally, if the R-Peak is positive, then the 'Q' and 'S' peaks will be negative and vice versa. In most of the feature extraction algorithms [3] have not considered in finding the negative side of 'Q 'and 'S ', losing the accuracy of the algorithm, where in the proposed method, we are able to find the 'Q 'and 'S 'points in a very accurate way.

Once we get the R-Peak index, we need to check whether the value of R-peak is positive or negative by passing the index value to the location of main memory (ECG memory). To find the 'Q 'index, we need to find the minimum value between the  $QRS_{on}$  and R-Peak when the R-peak is positive, else we need to find the maximum when the Rpeak is negative, the same case is applicable in finding the 'S 'point but the range changes from R-peak to  $QRS_{off}$ . The optimization is achieved in getting the P/T waves in terms of decreasing the computational complexity by removing unnecessary conditions [3]. Algorithms till date have tried to find the maximum and minimum for P/T peaks based on the conditions occurred after applying MMA on cD\_L5 coefficients, and other complex functions [3]. To explain the low complexity of the optimized algorithm, we have taken an example. Let 's say x\_1 and x\_2 are the maximum and minimum coefficients in the cD\_L5 coefficients in the range of '1'to  $(QRS_{on} >> 2$ , right shift by two times) then, irrespective of whether x\_1 index is greater than x\_2 or vice versa, we can directly go to main memory (4096 samples) and find the absolute value between the range (P\_on =  $x_1 << 5$ ) and  $(P_off = x_2 << 5)$  for getting P peak index, please see the line number of 11 of Algorithm 2. This logic avoid the extra hardware architecture required for holding the conditions (whether  $x_1 > x_2$  or  $x_1 < x_2$ ) and while implementing we have not used any bulky hardware like multipliers and shifters, instead we have appended that many number of zeroes to get the same value. The same procedure is followed in finding the T peak, T\_on and T\_off indices, whereas the ranges change from  $(QRS_{off} >> 2)$  to cD\_15\_end (last sample in cD\_L5) for the detailed coefficients of fifth resolution level, please see the line number of 11 of Algorithm 14. The above mentioned pseudo code is for one frame and it applies to all other frames got from boundary detection algorithm as shown in Fig.4 (b).

## III. RESULTS AND DISCUSSIONS

The combined validation of the whole system is performed using the AMS simulator of Cadence Virtuoso. The input (ECG) is given in pwl format and fed it to the analog block. The digital output from ADC is fed to the digital block and the input and output waveforms of the entire system are monitored on the AMS simulator for the verification.

Switching of ADC resolution from low (8 bit) to high (12 bit) occurs only when there is any abnormal in heart rate count. Initially the outcome of ADC is an 8 bit ECG data, the digital block will process the data and if any variation in the heart rate count compared to the normal condition of the patient then the control signal from the digital block will act as a switch to change the resolution of the ADC to 12 bit to maintain the accuracy in the classification of ECG while extracting the features. The reason for choosing 8-bit resolution is to reduce the power consumption of the chip while processing. Even at the 8-bit resolution we can easily track the heart rate of the patient without losing the accuracy in calculating the heartbeat count. However, after the abnormal

heart rate detection, to maintain the accuracy of classification in extracting the features of ECG we go for high resolution (12 bit) of the ECG data. Therefore, any abnormal variation in the heart rate count leads to the switching from low resolution to high resolution of the ADC. The digital module consumes 6.86  $\mu$ W and 7.47  $\mu$ W power at 1MHZ for 8 and 12 bit ECG data respectively.

# A. Analog Frontend Valiadtion

The complete analog module was validated on the ECG signal taken from the PTBDB [15], CSEDB [21] and IITHDB. The digital output of the  $\Sigma\Delta$  ADC (stream of 1s and 0s) generated by the Spectre simulator in cadence is exported to Matlab Simulink, where it is passed through a CIC filter to reconstruct the ECG signal. As is shown in Fig. 3 (b) the reconstructed waveform captures all the essential features of the ECG signal. The performance parameters of the designed AFE are compiled in Table II. Table III summarizes the performance of the designed  $\Sigma\Delta$  ADC.

TABLE II AFE PERFORMANCE

| Parameter                        | Value     |        |          |           |  |

|----------------------------------|-----------|--------|----------|-----------|--|

|                                  | This Work | [18]   | [19]     | [22]      |  |

| Technology (μm)                  | 0.18      | 0.35   | 0.35     | 0.18      |  |

| Voltage Supply (V)               | 1.8       | 2.5    | 1        | 1         |  |

| Power Consumption (µW)           | 0.47      | 0.62   | 0.9      | 0.8       |  |

| CMRR (dB)                        | 150       | 70     | 71.2     | 60        |  |

| Gain (dB)                        | 40-60     | 40.7   | 45.6-60  | 34        |  |

| Bandwidth (Hz)                   | 0.25-250  | 5m-200 | 4.5m-290 | 0.2-5.8 K |  |

| Input referred<br>Noise (u Vrms) | 5.2       | 2.8    | 2.5      | 5.71      |  |

TABLE III  $\label{eq:constraint} \text{Opamp shared } \Sigma\Delta \text{ ADC performance}$

| Parameter              | Value     |          |         |

|------------------------|-----------|----------|---------|

|                        | This Work | [16]     | [17]    |

| Technology (µm)        | 0.18      | 0.18     | 0.18    |

| Voltage Supply (V)     | 1.8       | 0.9      | 0.7     |

| Order                  | 2nd       | 2nd      | 2nd     |

| Bandwidth (Hz)         | 150       | 10 K     | 8 K     |

| Sampling Frequency     | 15.625 K  | 5 M      | 1.024 M |

| Power Consumption (µW) | 1.4       | 200      | 80      |

| SFDR/DR                | 76        | 83       | 75      |

| FOM1 (pJ/conv)         | 0.9050    | 0.8662   | 1.0879  |

| FOM2                   | 156.2996  | 159.9897 | 155     |

#### B. Proposed BD and FE Validation

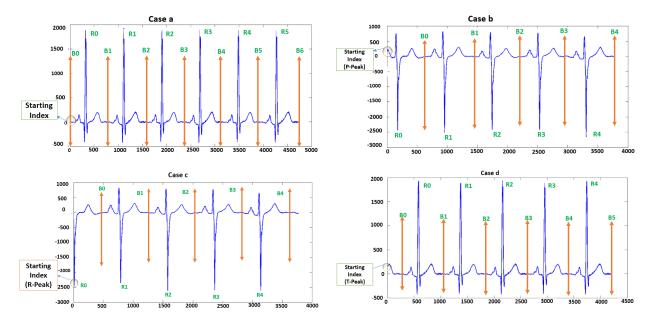

The validation has been done by testing the proposed methodology on 350 test cases of different ECG diseases (Myocardial Infraction, Hypertrophy, sinus arrhythmia, ventricular arrhythmias, etc.) and normal ECG signal database taken from PTBDB [15], CSEDB [21] and in-house IITHDB, these records are standard 12-lead ECG sampled at a rate of 1 KHz. The stability and the correctness of the proposed system is evaluated by the validating the whole system using the various

Fig. 5. Cases with different ECG input signal sensed at different index points (case a) ECG signal sensed from before onset of P (case b) Input signal sensing from P-peak. (case c) Input signal detection from R peak (case d) Sensing started from T-peak.

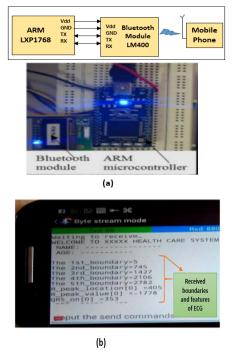

Fig. 6. (a)Block diagram of the proposed BD and FE system using ARM LPC1768 (b) Boundaries and features of the ECG signal received by the mobile phone

ECG normal and abnormal signals obtained from the ECG database [15], [21]. We have implemented the design on three platforms, ASIC, FPGA, and ARM board. The performance evaluation of BD and FE are shown in the TABLE IV and TABLE V respectively in terms of the mean and standard deviation of the error between the algorithm and the annotation result for each record. Overall mean and the standard deviation are calculated by taking the average of mean and the standard

deviation error of all the records. The design has been analyzed by customizing the ECG wave starting index with different case points (P, Q, R, S, and T) as shown in the Fig.5. All these cases have been given to the architecture and the outcome of boundaries and R-peaks are highlighted in the Fig. 5 resulting in 99% accuracy in detecting the proper boundaries and the extracting the features of the ECG signal.

The design is implemented on ARM cortex M3 based microcontroller LPC1768 which has 500 KB flash memory and 64 KB SRAM. The design is coded in embedded C and compiled for LPC 1768 using ARM mbed online compiler. The overall memory consumed for implementation is 39.1kB (8%) of flash and 0.7kB (2%) of RAM. After processing if the ECG signal is detected as abnormal by the rule engine logic [9], then the LED1 on LPC1768 board blinks and simultaneously sends patient fiducial points and ECG signal samples to the doctor mobile phone via Bluetooth as shown in Fig.6. Verilog code is written for the integration of BD and FE, where the Xilinx ISE tool is used to verify the results, we have used Xilinx inbuilt memory core (BRAM) in storing the ECG samples and the DWT coefficients. The BIT file is downloaded onto the Xilinx Virtex-7 FPGA chip using JTAG cable, the final results from the FPGA have been observed on the Chipscope pro tool. The design has occupied 19 % of the slice LUTs present in the Virtex-7 board. The proposed

system is implemented in 180 nm technology resulting in  $9.47\mu W$  (@ 1 MHz) power consumption and occupying  $1.74\,mm^2$  silicon area. Table VI summarizes the comparison study with our proposed work and the state-of-the-art ECG-based cardiac health monitoring architectures. However, it is to be noted that among the existing architectures (Table VI), [7] focused only on the artifacts removal and R-peak detection but not on extracting features and classification of ECG. [8] has achieved comparable power consumption like the proposed one, but the application is limited to ECG acquisition and the

TABLE IV

PERFORMANCE RESULTS OF PROPOSED BD

| Database      | Performance Metric | Start Boundary | End Boundary | Patients Data |  |

|---------------|--------------------|----------------|--------------|---------------|--|

|               | # ann beats        | 10,500         | 10,500       | D_00001       |  |

| CSE DB        | u+-s (ms)          | 4+-5.2         | 3+-4.7       | D_00002       |  |

|               | sigma (Samples)    | 5              | 4            | D_00003       |  |

|               | % Error FBD        | 0.0            | D_00004      |               |  |

| PTBDB         | # ann beats        | 1950           | 1950         | S000_1re      |  |

|               | u+-s (ms)          | 3+-4.5         | 3.5+-3.8     | S000_2re      |  |

| 1 1000        | sigma (Samples)    | 4 7            |              | S000_3re      |  |

|               | % Error FBD        | 0.03%          |              | S000_4re      |  |

| IITH Database | # ann beats        | 750            | 750          | #1            |  |

|               | u+-s (ms)          | 7+-9.1         | 5+-7.2       | #2            |  |

|               | sigma (Samples)    | 9 10           |              | #3            |  |

|               | % Error FBD        | 0.06%          |              | #4            |  |

${\bf TABLE\ V}$  Performance Results of FE on the Databases, DB: Data Base, PM: Performance Metric

| DB                  | PM        | Pon      | Ppeak       | Poff      | QRSon          | Rpeak  | QRSoff        | Ton       | Tpeak          | Toff     |

|---------------------|-----------|----------|-------------|-----------|----------------|--------|---------------|-----------|----------------|----------|

| PTBDB               | ann beats | 1950     | 1950        | 1950      | 1950           | 1950   | 1950          | 1950      | 1950           | 1950     |

|                     | u±s (ms)  | 1.8±7.8  | 4.2±8.4     | -5.2±9.9  | $4\pm10.3$     | 1±2.4  | 3.4±7         | -7.8±11.1 | $-7.5\pm11.3$  | -6.9±8.8 |

| CSEDB               | ann beats | 10,500   | 10,500      | 10,500    | 10,500         | 10,500 | 10,500        | 10,500    | 10,500         | 10,500   |

|                     | u±s (ms)  | -3.8±7.5 | $4.1\pm7.8$ | 2.1±5     | $1\pm 5.9$     | 1±2.2  | $4.9 \pm 8.8$ | -8.3±10.7 | $-10.1\pm12.4$ | 3.1±11.9 |

| IITHDB              | ann beats | 750      | 750         | 750       | 750            | 750    | 750           | 750       | 750            | 750      |

|                     | u±s (ms)  | 7.8±9.9  | 5.3±9.3     | -4.2±10.2 | $3.5\pm11.3$   | 1±3.4  | 7±10.9        | -5.3±11.2 | $-7.1\pm10.3$  | 4.4±13.2 |

| Mazomenos [3] PTBDB | ann beats | 422      |             | 422       | 450            |        | 450           |           |                | 432      |

|                     | u±s (ms)  | 1.1±9.5  |             | -6±11     | $3.8 \pm 10.8$ |        | 3.7±6.8       |           |                | -8±10.8  |

| CSE [21]            | 2 sigma   | 10.2     |             | 12.7      | 6.5            |        | 11.6          |           |                | 30.6     |

TABLE VI SUMMARY OF POWER ANALYSIS

| Parameter                 | Proposed Work | [7]      | [8]          | [23]       | [24] |

|---------------------------|---------------|----------|--------------|------------|------|

| Power Consumption µW      | 9.47          | 32       | 16.44        | 77         | 345  |

| Operating Frequency (MHZ) | 1             | 1        | 24           | 25         | 1-20 |

| Technology Node (µm)      | 0.18          | 0.18     | 0.13         | 0.9        | 0.18 |

| Voltage Supply (V)        | 1.8           | 1.2      | 1.2          | 1.0        | 1.2  |

| Area                      | $1.74 \ mm^2$ | $5 mm^2$ | $6.9 \ mm^2$ | 2.5x1.9 mm |      |

heart rate monitoring only without detailed feature extraction.

## IV. CONCLUSION

This paper presents a mixed-signal system for personalized and remote cardiac health monitoring. We proposed here novel methodologies to reduce the power consumption of the chip. Subsequently, the architecture based on the proposed methodology has been designed and performance has been compared with the state-of-the-art designs. Low power analog front end with an efficient automatic gain control mechanism, maintaining the input of the ADC to a level rendering optimum SNR and the enhanced recyclic folded cascode opamp used as an integrator for  $\Sigma\Delta$  ADC is our first contribution. Secondly, a novel on-the-fly PQRST BD methodology is formulated for finding the boundaries. A novel low-complexity ECG feature extraction architecture is designed by reusing the same module present in the proposed BD methodology is our third contribution. As shown in the Section III, the results obtained from the proposed system have the medical significance in terms of detecting abnormal ECG waves. The proposed system is having the capability to reconfigure the ADC from low (8 bit) to high (12 bit) resolution using a feedback signal from the digital block is our fourth contribution. We have taken the ECG database from the PTBDB, CSEDB and in-house IIT Hyderabad DB (IITHDB) to validate the whole system and we got an accuracy of 99% upon testing on various healthy and unhealthy ECG signals. The whole design is occupying an area of 1.74  $mm^2$  and consume 9.47 $\mu$ W (@ 1 MHz) power using the technology node of 180nm.

# ACKNOWLEDGMENT

The project is partly funded under the "Internet Of Things (IOT) for Smarter Healthcare" project under Grant No: 13(7)/2012-CCBT, Ministry of Electronics and Information Technology, Govt. of India dated 25th February, 2013. All VLSI Computer Aided Design tools used in this work were supported under "Special Manpower Development Program for Chips to System Design (SMDP-C2SD) Ministry of Electronics and Information Technology, Govt. of India". Amit Acharyya would also like to acknowledge his "Visvesvaraya Young Faculty Fellowship" by the Ministry of electronics and Information Technology, Govt. of India.

#### REFERENCES

[1] CVD statistics as per WHO. [Online]. Available: http://www.who.int/cardiovascular\_diseases/en/

- [2] Wu, C.-C.; Kuo, W.-C.; Wang, H.-J.; Huang, Y.-C.; Chen, Y.-H.; Chou, Y.-Y.; Yu, S.-A.; Lu, S.-S., A pliable and batteryless real-time ECG monitoring system-in-a-patch, in VLSI Design, Automation and Test (VLSI-DAT), 2015 International Symposium on , vol., no., pp.1-4, 27-29 April 2015.

- [3] Mazomenos, E.B.; Biswas, D.; Acharyya, A.; Taihai Chen; Maharatna, K.; Rosengarten, J.; Morgan, J.; Curzen, N., "A Low-Complexity ECG Feature Extraction Algorithm for Mobile Healthcare Applications," Biomedical and Health Informatics, IEEE Journal of, vol.17, no.2, pp.459,469, March 2013.

- [4] Yao Zou; Jun Han; Xinqian Weng; Xiaoyang Zeng, "An Ultra-Low Power QRS Complex Detection Algorithm Based on Down-Sampling Wavelet Transform," in Signal Processing Letters, IEEE, vol.20, no.5, pp.515-518, May 2013.

- [5] Taihai Chen; Mazomenos, E.B.; Maharatna, K.; Dasmahapatra, S.; Niranjan, M., "Design of a Low-Power On-Body ECG Classifier for Remote Cardiovascular Monitoring Systems," in Emerging and Selected Topics in Circuits and Systems, IEEE Journal on , vol.3, no.1, pp.75-85, March 2013.

- [6] Sidek, K.A.; Khalil, I.; Jelinek, H.F., "ECG Biometric with Abnormal Cardiac Conditions in Remote Monitoring System," in Systems, Man, and Cybernetics: Systems, IEEE Transactions on , vol.44, no.11, pp.1498-1509, Nov. 2014

- [7] Hyejung Kim, Sunyoung Kim, Van Helleputte, N Artes, A.; Konijnenburg, M.; Huisken, J.; Van Hoof, C.; Yazicioglu, R.F., "A Configurable and Low-Power Mixed Signal SoC for Portable ECG Monitoring Applications," Biomedical Circuits and Systems, IEEE Transactions on , vol.8, no.2, pp.257,267, April 2014.

- [8] S. Izumi et al., "A Wearable Healthcare System With a 13.7  $\mu$  A Noise Tolerant ECG Processor," in IEEE Transactions on Biomedical Circuits and Systems, vol. 9, no. 5, pp. 733-742, Oct. 2015.

- [9] M. P. R. S. Kiran, P. Rajalakshmi, K. Bharadwaj and A. Acharyya, "Adaptive rule engine based IoT enabled remote health care data acquisition and smart transmission system," Internet of Things (WF-IoT), 2014 IEEE World Forum on, Seoul, 2014, pp. 253-258.

- [10] Assaad, R.S., Silva-Martinez, J., "The Recycling Folded Cascode: A General Enhancement of the Folded Cascode Amplifier," IEEE JSSC, vol.44, no.9, pp.2535, 2542, Sept. 2009.

- [11] P.; Kumaravel, S.; Venkatramani, B., "An enhanced fully differential Recyclic Folded Cascode OTA," 9th International Multi-Conference on Systems, Signals and Devices (SSD), 2012, vol., no., pp.1, 5, 20-23 March 2012

- [12] Ng, K.A; Yong Ping Xu, "A Compact, Low Input Capacitance Neural Recording Amplifier, IEEE TBCS, vol.7, no.5, pp.610, 620, Oct. 2013.

- [13] Yu-Cheng Su, Shuenn-Yuh Lee and An-Po Lin, "A 0.6-V 1.8-W automatic gain control circuit for digital hearing aid," Circuits and Systems, 2008. APCCAS 2008. IEEE Asia Pacific Conference on, Macao, 2008, pp. 113-116.

- [14] Zanbaghi, R.; Saxena, S.; Temes, G.C.; Fiez, T.S., "A 75-dB SNDR, 5-MHz Bandwidth Stage-Shared 22 MASH ΣΔ ADC Modulator Dissipating 16 mW Power," IEEE Transactions on Circuits and Systems I: Regular Papers, vol.59, no.8, pp.1614, 1625, Aug. 2012.

- [15] Goldberger AL, Amaral LAN, Glass L, Hausdorff JM, Ivanov PCh, Mark RG, Mietus JE, Moody GB, Peng C-K, Stanley HE. PhysioBank, PhysioToolkit, and PhysioNet: Components of a New Research Resource for Complex Physiologic Signals. Circulation 101(23):e215-e220 [Circulation Electronic Pages; http://circ.ahajournals.org/cgi/content/full/101/23/e215]; 2000 (June 13)

- [16] Goes, J.; Vaz, B.; Monteiro, R.; Paulino, N., "A 0.9V /spl Delta//spl Sigma/ Modulator with 80dB SNDR and 83dB DR Using a Single-Phase Technique," IEEE ISSCC, 2006. Digest of Technical Papers., vol., no., pp.191, 200, 6-9 Feb. 2006.

- [17] Sauerbrey, J.; Tille, T.; Schmitt-Landsiedel, D.; Thewes, R., "A 0.7V MOSFET-only switched-opamp /spl Sigma//spl Delta/ modulator, IEEE ISSCC. 2002, vol.2, no., pp.246, 492, 7-7 Feb. 2002.

- [18] Tzu-Yun Wang; Min-Rui Lai; Twigg, C.M.; Sheng-Yu Peng, "A Fully Reconfigurable Low-Noise Biopotential Sensing Amplifier with 1.96 Noise Efficiency Factor," IEEE TBCS, vol.8, no.3, pp.411, 422, June 2014.

- [19] Xiaodan Zou; Xiaoyuan Xu; Libin Yao; Yong Lian, "A 1 -V 450-nW Fully Integrated Programmable Biomedical Sensor Interface Chip," IEEE JSSC, vol.44, no.4, pp.1067,1077, April 2009.

- [20] Ng, K.A; Yong Ping Xu, "A Compact, Low Input Capacitance Neural Recording Amplifier, IEEE TBCS, vol.7, no.5, pp.610, 620, Oct. 2013.

- [21] The CSE working party, Recommendations for measurement standards in quantitative electrocardiography, Eur Heart J., vol. 6, no. 10, pp. 815825, Oct 1985.

- [22] L. Liu, X. Zou, W. L. Goh, R. Ramamoorthy, G. Dawe and M. Je, "800 nW 43 nV/Hz neural recording amplifier with enhanced noise efficiency factor," in Electronics Letters, vol. 48, no. 9, pp. 479-480, April 26 2012.

- [23] S. Y. Hsu, Y. Ho, P. Y. Chang, C. Su and C. Y. Lee, "A 48.6-to-105.2 W Machine Learning Assisted Cardiac Sensor SoC for Mobile Healthcare Applications," in IEEE Journal of Solid-State Circuits, vol. 49, no. 4, pp. 801-811, April 2014.

- [24] N. Van Helleputte et al., "A 345 W Multi-Sensor Biomedical SoC With Bio-Impedance, 3-Channel ECG, Motion Artifact Reduction, and Integrated DSP," in IEEE Journal of Solid-State Circuits, vol. 50, no. 1, pp. 230-244, Jan. 2015.

- [25] Puddu PE, D Alessandra A, Scarparo P, Centaro E, Torromeo C, Schiariti M, et al. A Clinician's View of Next-Generation Remote Healthcare System. In: Maharatna K, Bonfiglio S, editors. Systems Design for Remote Healthcare. Springer New York, 2014. p, 1-30 (DOI: 10:1007/978-1-4614-8842-2 1)

- [26] Acharyya A, Signal Processing Architecture Implementation Methodologies for Next-Generation Remote Healthcare Systems. In: Maharatna K, Bonfiglio S, editors. Systems Design for Remote Healthcare. Springer New York, 2014. p, 1-30 (DOI: 10:1007/978-1-4614-8842-21)