# Modeling a IF Double Sampling Bandpass Switched Capacitor $\Sigma\Delta$ ADC with a Symmetric Noise Transfer Function for WiMAX/WLAN

Pankaj Kumar Jha

Dept. of Electrical Engineering

IIT Hyderabad

Hyderabad, India

jovialjha@gmail.com

Nithin Kumar Y.B

Dept. of Electrical Engineering

IIT Kharagpur

Kharagpur, India

nithin.shastri@gmail.com

Abstract-4G technology aims to revolutionize private and professional communication with its ubiquity and high-speed transmission (averaging 100Mbps). WiMAX and WLAN are two of the high speed access technologies to be used in the 4G mobile communication. Apropos to their high bandwidths, oversampling converters, e.g.ΣΔ ADCs, used for these standards would entail high levels of power consumption. Double sampling technique used in  $\Sigma \Delta$  ADCs help in reducing the power consumption, since the actual sampling rate is only half the sampling frequency required to achieve a target resolution. But for conventional modulators, with low pass noise transfer functions (NTF), this benefit is hampered by the introduction of folded noise due to the mismatch of sampling capacitances. This paper presents a novel method of designing IF bandpass switched capacitor (SC) $\Sigma\Delta$ modulators with symmetric NTFs. Such a bandpass NTF is formulated with its center frequency at one-fourth the effective sampling frequency. The symmetricity ensures that the folded noise is 'noise-shaped' along with the quantization noise. The idea is verified with a discrete time bandpass  $\Sigma\Delta$  modulator modeled using Simulink®, including various nonlinearities, viz. clock jitter, opampnonidealities, and capacitive mismatch effects owing to double sampling and use of a multibitquantizer. Behavioral simulations of the proposed non-ideal model for WiMAX and WLAN, with a bandwith of 10MHz and 11MHz, respectively, achieved a peak resolution greater than 10 bits for each of the standards.

Keywords-4G mobile communication, A/D converter modeling, Delta-sigma modulation, double sampling, noise folding, nonlinearities.

# I. INTRODUCTION

4G, or the fourth generation of mobile communications standards, intents to conjoin a plethora of different services, modes, and hence, the corresponding different standards in different parts of the world. It promises the user a multitude of facilities, viz. localized/personalized information (e.g. general news, financial news, location guides, mobile commerce and

Ashudeb Dutta

Dept. of Electrical Engineering

IIT Hyderabad

Hyderabad, India

asudeb\_dutta@iith.ac.in

Shiv Govind Singh Dept. of Electrical Engineering IIT Hyderabad Hyderabad, India sgsingh@iith.ac.in

travel services), communications (e.g. short messaging service, e-mail, video conferencing, fax and bulletin boards), organizational (personal digital assistant capabilities, currency exchange based on user location and other personal management application) and entertainment (streaming audio, streaming video, chat, photo trading and gaming)[1]. It promises the user ten times larger capacity than 3G systems, average data rates of 100Mbps and seamless "always best connected" networking at system costs 1/10 ~ 1/100 of 3G systems [2]-[4]. WiMAXand WLAN are two key proponents of 4G communication, both being high bandwidth technologies. Power consumption is one of the prime concerns for systems designed for these high speed access technologies. This beseeches the designers to come up with systems consuming low power, or, to find techniques to reduce power consumption in the existing designs.

Figure 1. Generic scheme of a  $\Sigma\Delta$  modulator

$\Sigma\Delta$  modulator(Fig. 1) is an ubiquitous choice for high resolution A/D converters (*vis a vis* their other popular counterparts like the flash and SAR ADC) owing to their excellent ability to alleviate quantization noise in the frequency band of interest (endowed to them because of the combined effect of oversampling and noise-shaping) and robustness to circuit nonlinearities. The equation for the dynamic range (DR) of a  $\Sigma\Delta$  modulator is given by

dynamic range (DR) of a

$$\Sigma\Delta$$

modulator is given by

$$DR \approx \frac{3}{2} \left( \frac{2L+1}{\pi^{2L}} \right) (OSR)^{2L+2} (2^{B}-1)^{2}$$

(1)

where *L* is the order of the modulator, *OSR* is the oversampling ratio, and *B* is the number of bits of the internal quantizer. It is

2012 5th International Conference on Computers and Devices for Communication (CODEC) evident from (1) that it gives the designer higher degrees of freedom for design, since a target resolution can be achieved by an optimal choice of these parameters. Application speeds of  $\Sigma\Delta$  modulators vary from lesser than 6ksps and 10Msps for 24 bits and 16-18 bits of resolution,respectively.  $\Sigma\Delta$  ADCs find enormous applications in systems designed for reconfigurableIF and RF communication systems for multistandard wideband 'next-generation' 4G communication.

Double sampling is a technique which used to reduce the power consumption in the  $\Sigma\Delta$  ADCs. Both, sampling and integration are done on both the phases of the master clock. In this way, the effective sampling rate becomes twice the frequency of the master clock. Hence, a target resolution is achieved incurring lower power consumption. But this technique is impeded by the mismatch in the sampling capacitances. For the case of conventional  $\Sigma\Delta$  modulators, with low pass NTF, this path mismatch results in the quantization noise getting folded back from the half the sampling frequency into the signal band [12]. Various strategies have been implemented to deal with this folded noise, viz. dynamic mismatch techniques [5]-[6], using a bilinear input integrator [7]-[9], and using a modified NTF [10]-[12].

This paper presents a yet another scheme of using a modified NTF while using double sampling technique. It points out that a symmetric NTF can be synthesized if the center frequency of the bandpass  $\Sigma\Delta$  modulator is at 0.25fs, where fsis the effective sampling rate achieved with double sampling. Such an NTF, noise shapes the folded noise along with the quantization noise, hence significantly reducing the folded noise in the frequency band of interest. The behavioral simulations using the Simulink model of a bandpass  $\Sigma\Delta$ modulator, with nonlinearities incorporated and having a symmetrical NTF discussed above, vindicates that excellent resolutions can be obtained for high bandwidth(10-11MHz) standards like WiMAX and WLAN. The concept of having a bandpass NTF with center frequency at fs/4 is not a new idea. Designers normally choose IF at that location keeping the subsequent design of the decimation filter in mind. To the best of our knowlwdge, this is the first claim that such an NTF can also be used to alleviate the problem of folded noise in the frequency band of interest.

# II. Symmetric NTF for Double sampled $\Sigma\Delta$ modulators

Following the convention used in Rosa *et. al* [13], the *z*-domain equation for the final output can be written as

$$Y(z) = STF(z) * X(z) + NTF(z).$$

(2)

where STF(z) is the signal transfer function, X(z) is the input signal, NTF(z) is the noise transfer function and E(z) is the quantization error. Contribution of the quantization noise in the output is

$$Y_{\mathcal{O}}(z) = NTI(3)$$

A simplistic depiction of the integrator used in the double sampling modulators is shown in [12]. Here both sampling and integration actions occurs at both the phases of the master clock. The net result is that

$$f_{effective} = 2 * f_{m_e} \tag{4}$$

Hence, a target resolution can be achieved at half the theoretical OSR, saving significant amount of power.

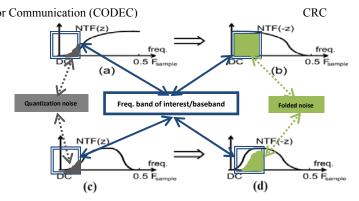

Figure 2. (a) NTF and (b) folded NTF of a conventional low pass  $\Sigma\Delta$  modulator. The corresponding shaded regions regions represent the quantization noise(grey) and the folded noise(light green). (c) NTF and (d) folded NTF of the same modulator with an additional zero inserted at f=fs/2. The corresponding noises are also depicted by the shaded region – reduction in the folded noise in the band of interest is evident.

On the dark side, this technique is impeded by the introduction of folded noise into the band of interest. A quantitative expression for this additional noise is (as is given in [11])

$$N_{Folid}(z) \approx \delta * E(-z)NTF(-z); \delta = \frac{(c_{z,1}-c_{z,1})}{(c_{z,1}+c_{z,2})}$$

(5)

where is the sampling capacitance mismatch. Fig. 2a and 2b shows the NTF, and corresponding folded NTF of the normal low pass  $\Sigma\Delta$  modulator along with the noises pointed out. It is apparent that folded noise is not small in the baseband. Rombouts *et. al* [12] proposes an idea wherein an additional zero is inserted at z=-1 (or  $\theta$ = $\pi$ , or f=fs/2). The benefit of reducing the folded noise in the baseband can be easily comprehended from the illustration (Fig. 2c and 2d).

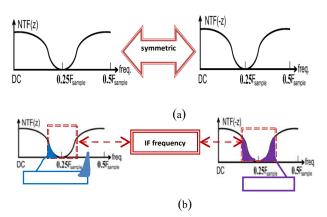

Figure 3. (a)NTF and folded NTF of the proposed scheme with symmetric NTF. (b) The corresponing noises in the band of interest are also shown.

This paper intends to show that an analogous leverage can be achieved by using a bandpass NTF with its center frequency at fs/4. Fig. 3 illustrates the NTFs and the corresponding noises for this strategy. It is pretty clear that folded noise is "noise-shaped" along with the quantization noise. The advantage of this scheme over that proposed in [12] is that no additional zeros need to be inserted, hence saving any extra hardware and power.

# III. System level modeling of a nonlinear bandpass SC $\Sigma\Delta$ modulator with symmetric NTF

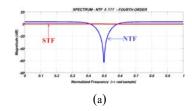

To start with, the modulator specifications are adopted from [14]. The chosen specifications are summarized in the Table I. A  $\Sigma\Delta$  modulator for these specifications is modeled using Simulink. The NTF is formulated using the 'cookbook' procedure in [15], [16]. The 4<sup>th</sup> order bandpass NTF and STF used here is

$$NTF(z) = \frac{(z^2 + 1)^2}{(z^2 - 0.3222z + 0.664z^3)(z^2 + 0.3222z + 0.64}$$

$$STF(z) = 1$$

(6)

Fig. 4a shows the magnitude plot of the NTF. The NTF is synthesized using cascade-of-resonatorsfeedforward form (CRFF) topology (Fig. 4b), preferably because of its universal usage[15].

The 'cookbook' procedure allows us to have our STF equal to unity. This reduces the signal swings at the input/output of the integrators in the loop filter, relaxing their linearity

TABLE I.  $\Sigma\Delta$  modulator model parameters

| D                                            |                  | Value              |         |  |

|----------------------------------------------|------------------|--------------------|---------|--|

| Parameter                                    |                  | WiMAX              | WLAN    |  |

| Order of the modulator                       |                  | 4                  | 4       |  |

| OSR <sup>1</sup>                             |                  | 16                 | 16      |  |

| Number of bits in the internal quantizer     |                  | 4                  | 4       |  |

| IF center frequency                          |                  | 80 MHz             | 80MHz   |  |

| Sampling frequency (fs) <sup>1</sup>         |                  | 320MHz             | 320MHz  |  |

| Bandwidth (BW)                               |                  | 10 MHz             | 11MHz   |  |

| Target ENOB <sup>2</sup>                     |                  | 8-14               | 7-11    |  |

| Input amplitude                              |                  | -2.3 dB            | -2.3 dB |  |

| Input signal frequency (fin)                 |                  | 80MHz              | 80MHz   |  |

| Nonlinearities incorporated into the model   |                  |                    |         |  |

| Circuit nonlinearity                         | Value            |                    |         |  |

| Finite DC gain <sup>3</sup>                  | 100 dB           |                    |         |  |

| $GBW^3$                                      | 1000 MHz         |                    |         |  |

| Slew rate <sup>3</sup>                       | 574 V/μs         |                    |         |  |

| Capacitor mismatch of quantizer <sup>4</sup> |                  | $\sigma = 0.496$   |         |  |

|                                              |                  | $N_{COMP} = 15$    |         |  |

|                                              |                  | $C_{TOT} = 1.5 pF$ |         |  |

| Sampling capacitor mismatch <sup>4</sup>     | $\delta = 0.1\%$ |                    |         |  |

| Clock jitter <sup>4</sup>                    | 1ps              |                    |         |  |

<sup>1.</sup> Values in the table are double that mentioned in [15], taking into account the effect of double sampling. Actual fs = 160 MHz, 2. Effective number of bits, c. Adopted from [15], d. Adopted from [16]

requirements, hence reducing static power consumption in the actual circuit. Also, since for unity-STF  $\Sigma\Delta$  ADCs the integrator outputs are independent of the input, single stage opamps are sufficient to implement the analog filter, hence further reducing the powers [22],[23].

Figure 4. (a) Magnitude plot of the proposed NTF and STF (b) The generic even order CRFF topology used to model the loop filter of the  $\Sigma\Delta$  modulator [15].

The various sources of nonlinearities are also incorporated into the design. The models are adopted from [18],[19]. The model of the nonideal quantizer is taken from the toolbox available in [21]. The mismatch due to the sampling capacitances in double sampling is modeled using the concept mentioned in [17] and [20].

# IV. SIMULATION AND RESULTS

Two different Simulink models of the  $\Sigma\Delta$  modulator are obtained following the procedure and specifications discussed in the previous section. The first one is an ideal system, built from all the ideal blocks. The second one is a nonlinear system, which includes all the nonidealities mentioned in Table I. Both the systems were simulated for the targeted WiMAX (BW = 10MHz) and WLAN (BW = 11MHz) standards.

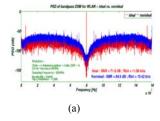

The behavioral simulations for WiMAX achieved a peak SNR of 73.4dB and 64.7dB for the ideal and the nonideal model respectively (Fig. 5).

Figure 5. (a) PSD plot of the  $\Sigma\Delta$  modulator for WiMAX standard – ideal (red) and nonideal (blue). (b) A zoomed-in view of the PSD for the frequency band of interest i.e. from 75-85MHz (BW = 10MHz).

Similar simulations were caried out for the WLAN standard. The results reveal that a peak SNR of 71.3dB and 64.5dB can be obtained from the ideal and nonideal modulator respectively (Fig. 6).

Figure 6. (a) PSD plot of the ΣΔ modulator for WLAN standard – ideal (red) and nonideal (green). (b) A zoomed-in view of the PSD for the frequency band of interest i.e. from 74.5-85.5MHz (BW = 11MHz).

The behavioral simulations show that the targets set for SNR values, set in the beginning of the previous section, can be achieved using the model proposed in this paper. Also, Fig. 5b and 6b reveal that the PSD is devoid of any menacing tones in the frequency band of interest. Table II summarizes the performance of this work along with a couple of other related works.

TABLE II. PERFORMANCE SUMMARY

|                            | Reference & year of publication       |                      |            |

|----------------------------|---------------------------------------|----------------------|------------|

| ΣΔ modulator<br>parameters | [17];2011                             | [24];2010            | This work  |

| Topology                   | Bandpass with                         | 2-1-1 cascade        | CRFF       |

|                            | tunable resonators and noise-coupling | with low pass<br>NTF |            |

| Quantizer (bits)           | 4                                     | 1bit for all         | 4          |

|                            |                                       | stages               |            |

| BW(MHz)                    | WLAN: 20                              | WLAN: 22             | WLAN: 11   |

|                            | WiMAX :                               | Wimax : 28           | Wimax: 10  |

| SNDR (dB)                  | Wlan: 55                              | Wlan : 57            | Wlan:64.5  |

|                            | Wimax :                               | Wimax : 48           | Wimax:64.7 |

| Order (effective)          | 6                                     | 4                    | 4          |

| OSR (effective)            | ≈12                                   | Wlan: 12             | Wlan : 16  |

|                            |                                       | Wimax: 10            | Wimax: 16  |

| Actual fs (MHz)            | 125                                   | WLAN: 132            | 160        |

|                            |                                       | WiMAX: 140           |            |

| IF Center frequency        | 62.5 MHz                              |                      | 80MHz      |

# V. CONCLUSION

A bandpass NTF with its center frequency at fs/4 is proposed to alleviate the folding noise in the frequency band of interest. A nonlinear model of SC  $\Sigma\Delta$  modulator with such a NTF is simulated using Simulink. The behavioral simulations affirm that system can be used for WiMAX and WLAN standards. A peak SNR of 64.7dB and 64.5dB is obtained for WiMAX and WLAN respectively. A logical step could be to try the same using quadrature  $\Sigma\Delta$  modulator, which is expected to give the similar results with a lower order loop.

# REFERENCES

- Emerging Wireless Technologies 4G Applications and Services,http://www.safecomprogram.gov/library/lists/library/DispForm .aspx?ID=226.

- [2] Tachikawa, K.; , "A perspective on the evolution of mobile communications," Communications Magazine, IEEE , vol.41, no.10, pp. 66-73, Oct 2003.

- [3] Gustafsson, E.; Jonsson, A.; , "Always best connected," Wireless Communications, IEEE , vol.10, no.1, pp. 49-55, Feb. 2003.

- [4] Frattasi, S.; Fathi, H.; Fitzek, F.H.P.; Prasad, R.; Katz, M.D.; , "Defining 4G technology from the users perspective," Network, IEEE , vol.20, no.1, pp.35-41, Jan.-Feb. 2006.

- [5] Burmas, T.V.; Dyer, K.C.; Hurst, P.J.; Lewis, S.H.; , "A second-order double-sampled delta-sigma modulator using additive-error switching,"

- Solid-State Circuits, IEEE Journal of , vol.31, no.3, pp.284-293, Mar 1996

- [6] Thanh, C.K.; Lewis, S.H.; Hurst, P.J.; , "A second-order double-sampled delta-sigma modulator using individual-level averaging," Solid-State Circuits, IEEE Journal of , vol.32, no.8, pp.1269-1273, Aug 1997.

- [7] Hong-Kui Yang, El-Masry, E.I.; , "Double sampling delta-sigma modulators," Circuits and Systems II: Analog and Digital Signal Processing, IEEE Transactions on , vol.43, no.7, pp.524-529, Jul 1996.

- [8] Senderowicz, D.; Nicollini, G.; Pernici, S.; Nagari, A.; Confalonieri, P.; Dallavalle, C.; , "Low-voltage double-sampled ΣΔ converters," Solid-State Circuits Conference, 1997. Digest of Technical Papers. 43rd.

- [9] Vleugels, K.; Rabii, S.; Wooley, B.A.; , "A 2.5-V sigma-delta modulator for broadband communications applications," Solid-State Circuits, IEEE Journal of , vol.36, no.12, pp.1887-1899, Dec 2001.

- [10] Rombouts, P.; Raman, J.; Weyten, L.; , "An efficient technique to eliminate quantisation noise folding in double-sampling  $\Sigma\Delta$  modulators," Circuits and Systems, 2002. ISCAS 2002. IEEE International Symposium on , vol.3, no., pp. III-707- III-710 vol.3, 2002.

- [11] Rombouts, P.; Raman, J.; Weyten, L.; , "An approach to tackle quantization noise folding in double-sampling  $\Sigma\Delta$  modulation A/D converters," Circuits and Systems II: Analog and Digital Signal Processing, IEEE Transactions on , vol.50, no.4, pp. 157- 163, Apr 2003.

- [12] Rombouts, P.; De Maeyer, J.; Weyten, L.; , "A 250-kHz 94-dB double-sampling ΣΔmodulation A/D converter with a modified noise transfer function," Solid-State Circuits, IEEE Journal of , vol.38, no.10, pp. 1657-1662, Oct. 2003.

- [13] R. del rio, F. Mediro, B.P. Verdu, J.M. de la Rosa, A.R. Vazquez, "CMOS Cascaded Sigma-delta Modulators for Sensor and Telecom – Error Analysis and Practical Design", Springer © 2006, ISBN-10: 1-4020-4776-2.

- [14] Artur Silva, Jorge Guilherme, Nuno Horta, Reconfigurable multi-mode sigma-delta modulator for 4G mobile terminals, Integration, the VLSI Journal, Volume 42, Issue 1, January 2009, Pages 34-46, ISSN 0167-9260, 10.1016/j.vlsi.2008.07.004.

- [15] http://www.mathworks.com/matlabcentral/fileexchange/19.

- [16] R. Schreier, G.C. Themes, Understanding Delta–Sigma Data Converters, Wiley, New York, 2005.

- [17] Hong Chang; Wenxian Lu; Xu Cheng; Yawei Guo; Xiaoyang Zeng; , "Modeling of a double-sampling switched-capacitor bandpass deltasigma modulator for multi-standard applications," ASIC (ASICON), 2011 IEEE 9th International Conference on , vol., no., pp.465-468, 25-28 Oct. 2011.

- [18] Brigati, S.; Francesconi, F.; Malcovati, P.; Tonietto, D.; Baschirotto, A.; Maloberti, F.; , "Modeling sigma-delta modulator non-idealities in SIMULINK(R)," Proceedings of the 1999 IEEE International Symposium onCircuits and Systems, 1999. ISCAS '99., vol.2, no., pp.384-387 vol.2, Jul 1999.

- [19] Fornasari, A.; Malcovati, P.; Maloberti, F.; , "Improved modeling of sigma-delta modulator non-idealities in Simulink," IEEE International Symposium on Circuits and Systems, 2005. ISCAS 2005., vol., no., pp. 5982-5985 Vol. 6, 23-26 May 2005.

- [20] T.Yamamoto, M.Kasahara etc, "A 63mA 112/94 dB DR IFBandpass  $\Sigma\Delta$  Modulator with Direct Feed-ForwardCompensation and Double Sampling", JSSC, p.1783(2008).

- [21] http://www.mathworks.de/matlabcentral/fileexchange/25811-sdtoolbox-2/content/SDtoolbox/SDtoolboxhelp/SDtoolbox\_product\_page.html.

- [22] Siu-Hong Lui; Ngai Wong; , "Systematic Power Minimization in Multibit Delta-Sigma Analog-to-Digital Converters," TENCON 2006. 2006 IEEE Region 10 Conference , vol., no., pp.1-4, 14-17 Nov. 2006.

- [23] Hamoui, A.A.; Martin, K.W.; "High-order multibit modulators and pseudo data-weighted-averaging in low-oversampling ΔΣ ADCs for broad-band applications," *Circuits and Systems I: Regular Papers, IEEE Transactions on*, vol.51, no.1, pp. 72-85, Jan. 2004.

- [24] Li Jinfeng; Tang Zhen'an; ,"A Reconfigurable Double Sampling Sigma Delta Modulator for 4G Wireless Receivers," *Communications and Mobile Computing (CMC)*, 2010 International Conference on , vol.3, no., pp.369-373, 12-14 April 2010.